The European Processor Initiative, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is finishing its second year of activities.

Despite 2020 bringing upon our young efforts the circumstances that were previously unimaginable, causing the subsequent cancellation of the first-ever planned European Processor Initiative Forum, the partners in the Initiative managed to stay the course and maintain all activities in all designated streams.

The year began with our latest partner, SiPearl, launching to start their activities dedicated to developing commercialized implementations of our technology. Very soon after announcing their presence on the global stage, SiPearl signed a licensing agreement with Arm and opened a branch in Germany.

At the same time, European Processor Initiative partners have finalized the first version of our RISC-V accelerator architecture, named EPAC, and we look forward to the delivery of the first European Processor Initiative silicon featuring EPAC Test Chip in the exciting year that follows. The EPAC Test Chip silicon will be complemented with PCIe EPAC Test Platform enabling the test and enhancements of the architecture for future revisions.

At the software level, we already have a compiler supporting RISC-V vector intrinsics and automatic parallelization of C/C++ codes. We are evaluating the generated code on emulation platforms that provide detailed insight for the holistic co-design of applications, compiler, and architecture. We also have other software development vehicles (SDV) where we are adapting the Operating System for the Heterogeneous ARM+RISC-V architecture of the European Processor Initiative project.

Our automotive activities in the previous year have been focused on the design of state-of-the-art automotive high-performance computing proof-of-concept with the ambition to demonstrate how European Processor Initiative IP will enable future ADAS functionality, paving the way to exploit the GPP, the RISC-V platform, the Kalray MPPA, and the Menta eFPGA IP.

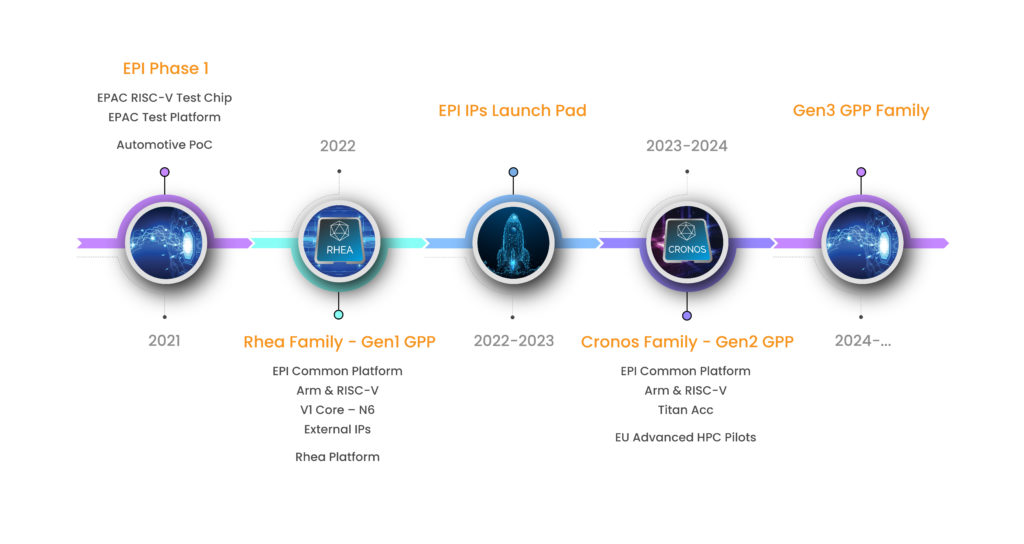

Based on this project progress, the Consortium is ready to announce the updated project roadmap shown below:

European Processor Initiative will, together with colleagues from other European exascale projects, attend the virtual Supercomputing20, where we will showcase our latest developments and update to the roadmap. We invite you to attend our virtual booth and join in the lively discussions about the future of HPC!

October started pretty busy for EPI partners, who attended various events presenting the latest from the Initiative.

The calendar was launched by members of Atos and CEA attending the RISC-V Week in Paris, which encompassed two major groups: The 2nd RISC-V Meetings, organized by IRT Nanoelec and CEA and The Scientific Day of IRT SE & GDR SOC2: RISC-V for critical embedded systems, organized by IRT St-Exupéry and GDR SOC2.

Romain Dolbeau from Atos gave a talk titled “European Processor Initiative: challenges & opportunities for RISC-V accelerators in an HPC platform”. He described the currently anticipated architecture of the EPI design and how to leverage this architecture in the software, using open standards. In particular, he touched upon how the EPI project is developing IP for a set of RISC-V-based accelerators designed to connect directly to the processor network-on-chip. He also discussed EPI plans to integrate those IPs in a silicon device, and how other accelerators IP designers could leverage EPI to create new high-performance multi-chip processing devices.

At that same event, Denis Dutoit from CEA gave a talk titled “European Processor Initiative: First step towards a made-in-Europe high-performance microprocessor”. After an introduction on High Performance Computing new challenges and associated technology/architecture evolution, the presentation highlighted the EPI position statement on generic computing, accelerator with RISC-V and design methodology. The presentation concluded with an explanation of EPI’s roadmap towards a wide range of applications from Exascale computing to embedded HPC.

Italian partners also had a very busy week presenting EPI in several workshops and distinguished lectures. Fabrizio Magugliani from E4 Computer Engineering presented at the workshop “Edge computing: Quando il Cloud è troppo lontano”, which confirmed the need for integrating the different streams of data (coming from IoT, the Edge, Industry 4.0 and similar sources) in a consistent view, including the pre-processing of data at the Edge and a HPC-powered analysis in a centralized facility, applying AI and HPDA techniques to the streams and then storing and capitalizing on the ‘knowledge’ extracted from the data. He introduced the roadmap and goals of the EPI and highlighted that the roadmap is fully consistent with the computational need of such a chain of processing.

Only two days later, he also presented at the 12th International Conference on Internet and Distributed Computing Systems in Naples. The speakers listed in the rich agenda detailed how the rapidly evolving technology for Distributed Computing Systems enables to use more computation and ‘intelligence’ at the Edge, and how to maximize the effectiveness of different architectures and components. While these components are ideal for analyzing data at the Edge, more elaborate analysis demands the use of more powerful systems. Having the same Instruction set at the Edge (running Arm devices) as well as in the centralized computing facility is definitely a value, making the EPI processor ideal for seamless integration of the data streams with the EPI-powered centralized facility.

Coming from EPI’s academic wing, University of Pisa’s Prof. Sergio Saponara was invited to give a lecture at the IEEE I&M France Chapter/GDR SoC2 Workshop. He held an IEEE IMS DL about ACES (autonomous, connected, electrified and shared) vehicles and related instruments and measurement/perception tools. The IEEE DL presented the opportunities and challenges of the ACES trends, with a focus on high-performance machine-perception sensors (like Radar, Lidar, Camera), navigation and positioning technologies (Inertial Measurement Units, Global Position/Navigation Satellite Systems). The challenge of the High-Performance Computing, needed on-board the vehicles to process in real-time such large amount of data, using either deterministic signal and data processing techniques or new machine learning and AI tools, have been also discussed. To this aim, the opportunities offered by EPI have been also presented.

Addressing the HPC user community, EPI Chair of the Board, Jean-Marc Denis, attended two HPC User Forums this week – the first in Lugano, Switzerland, and the second in Edinburgh, Scotland, where he presented the road so far, the latest developments and the Initiative future steps.

Across the ocean, another EPI industrial partner, Menta, attended the Arm TechCon in San Jose, California with their exhibition space at which they offered EPI materials for the interested attendees.

The automotive segment of EPI also had a busy week. Karlsruhe Institute of Technology held the first automotive summit in cooperation with the Tongji University in Shanghai. Many representatives from research and companies in China such as BMW, Infineon, Intron and UAES (Bosch in China) participated and gave interesting presentations about their current and future R&D projects. One major topic was autonomous driving and how it can be accomplished with the currently available computing resources, also with solutions ranging from edge and cloud computing to embedded HPC. This discussion naturally included KIT’s participation in EPI, which is why Prof. Jürgen Becker gave an interesting talk about the recent research activities in Germany and Europe also mentioning the on-goings in EPI and the known partners in the consortium. The project and plans were well received by the audience.

October schedule is still not finished, with several more events to go, all of which are announced at EPI’s web calendar: https://www.european-processor-initiative.eu/events/, serving as a perfect ramp-up to Initiative’s attendance at Supercomputing in Denver, US and EFECS conference in Helsinki, Finland in November. Meet us there!