The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 28 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies is proud to announce that we have successfully booted Linux on our EPAC 1.0 core subset implemented on FPGA.

One key segment of EPI activities is to develop and demonstrate fully European processor IPs based on the RISC-V Instruction Set Architecture, providing power efficient and high throughput accelerator core named EPAC (European Processor Accelerator). Using RISC-V will allow leveraging open-source resources at hardware architecture level and software level, as well as ensuring independence from non-European patented computing technologies.

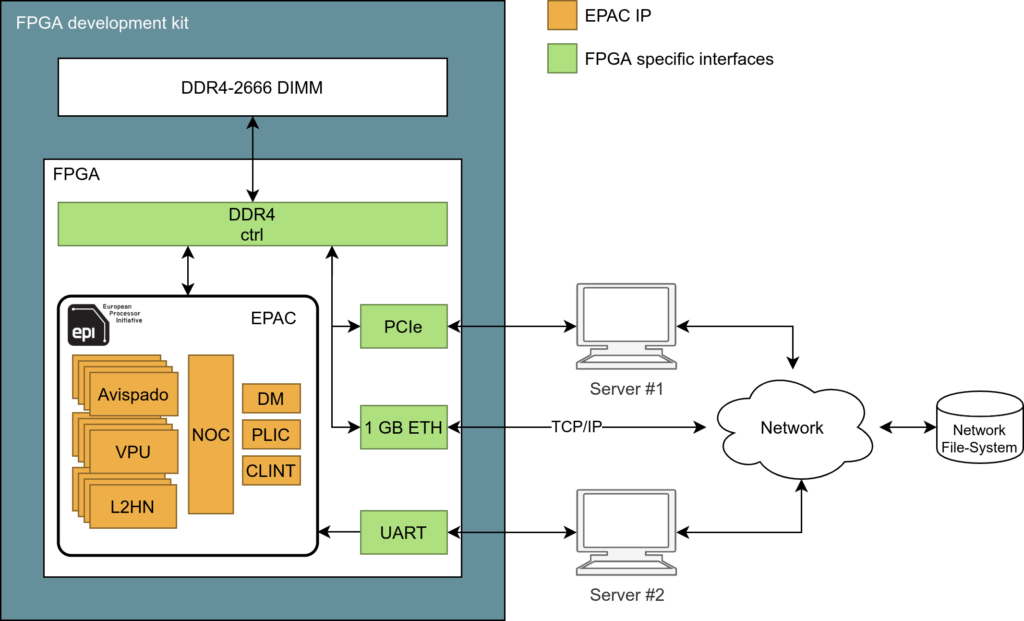

First silicon implementation of EPAC 1.0 test chip is expected in the second half of 2021 and as an important technical milestone towards that goal, we have successfully booted Linux on a subset of EPAC 1.0 synthesized on FPGA. The FPGA design includes the Avispado RISC-V core, the Vector Processing Unit (VPU), the Network on Chip (NoC), the Shared L2 Cache with Coherence Home Node (L2HN), interrupt controllers, IO peripherals and several other components. This implementation will enormously speed-up software development on the EPI HPC architecture as well as testing and improving the architecture for next generations EPAC chips.

For the development of the EPI Accelerator Test Chip, we make extensive use of FPGA technologies to verify the RTL design of the Test Chip. The subset of EPAC 1.0 emulated on FPGA we use as Software Development Vehicle (SDV) to enable early software development before the actual Test Chip silicon comes back from the foundry.

The use of FPGAs enables the testing of RTL blocks with real and very complex software in timescales that are not tractable using pure RTL simulation. Also, it allowed us to stress memory coherence and several related corner cases. We have managed to boot Linux using the EPAC 1.0 system on FPGA and the system boots within a few dozens of seconds compared to weeks using pure simulation. The system is fully usable and interactive for system software and application development and it also includes Ethernet connectivity to enable running large and complex software packages, e.g., OpenMP, MPI.

This is a serious proof of concept that gives us the confidence of a functional and viable future product.

More details on the results can also be found on EPI YouTube Channel, where you can find the second episode of EPI Talks podcast, themed with booting Linux:

Channel: https://www.youtube.com/c/EuropeanProcessorInitiative/featured

Video: https://www.youtube.com/watch?v=X4klPnBjstI

This year’s HiPEAC conference was supposed to be held in beautiful Budapest, from January 18th to 20th 2021. However, due to the persistent pandemic conditions, it had to be moved to a digital edition.

European Processor Initiative’s consortium gladly accepted the opportunity to participate, both as a sponsor and with a tutorial given to the attendees. Our tutorial was held on Monday, January 18th, and it involved the following topics and presenters:

- Denis Dutoit, CEA: EPI overview and introduction to tutorial topics

- Sergio Saponara, UNIPI: Hardware security module in the EPI GPP

- Fabrizio Magugliani, E4: Update of the PCIe boards as development testbed for EPI

- Lilia Zaourar, Tanguy Sassolas, CEA: SESAM/VPSim: fast and highly configurable simulation framework for the EPI processor

- Andrea Bartolini, Giovanni Bambini, UNIBO: Emulating the power controller of the HPC power management systems

The tutorial was very well attended, and the attendees had a lot of interesting questions.

In addition to the tutorial, the EPI team has also hosted a virtual Brazen booth, where students, young researchers, and other prospective employees popped in to ask questions about the project. From the industrial side of EPI, Fabrizio Magugliani presented EPI in the industrial session, while Jurgen Becker attended the WRC workshop and gave an invited talk that involved EPI as well.

All of the presentations from HiPEAC given by EPI members can be found in our repository:

https://www.european-processor-initiative.eu/dissemination-material/epi-at-hipeac-2021/, while the tutorial video is also available on our YouTube Channel: https://www.youtube.com/watch?v=4AYDc6THtcM&t=9476s.

Finally, a shout-out to organizers: even though the team is more than eager to participate in the next one, hopefully live, HiPEAC conference, we are thankful to organizers for such a wonderful experience and the opportunity to share our views and ideas.

The European Processor Initiative, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is finishing its second year of activities.

Despite 2020 bringing upon our young efforts the circumstances that were previously unimaginable, causing the subsequent cancellation of the first-ever planned European Processor Initiative Forum, the partners in the Initiative managed to stay the course and maintain all activities in all designated streams.

The year began with our latest partner, SiPearl, launching to start their activities dedicated to developing commercialized implementations of our technology. Very soon after announcing their presence on the global stage, SiPearl signed a licensing agreement with Arm and opened a branch in Germany.

At the same time, European Processor Initiative partners have finalized the first version of our RISC-V accelerator architecture, named EPAC, and we look forward to the delivery of the first European Processor Initiative silicon featuring EPAC Test Chip in the exciting year that follows. The EPAC Test Chip silicon will be complemented with PCIe EPAC Test Platform enabling the test and enhancements of the architecture for future revisions.

At the software level, we already have a compiler supporting RISC-V vector intrinsics and automatic parallelization of C/C++ codes. We are evaluating the generated code on emulation platforms that provide detailed insight for the holistic co-design of applications, compiler, and architecture. We also have other software development vehicles (SDV) where we are adapting the Operating System for the Heterogeneous ARM+RISC-V architecture of the European Processor Initiative project.

Our automotive activities in the previous year have been focused on the design of state-of-the-art automotive high-performance computing proof-of-concept with the ambition to demonstrate how European Processor Initiative IP will enable future ADAS functionality, paving the way to exploit the GPP, the RISC-V platform, the Kalray MPPA, and the Menta eFPGA IP.

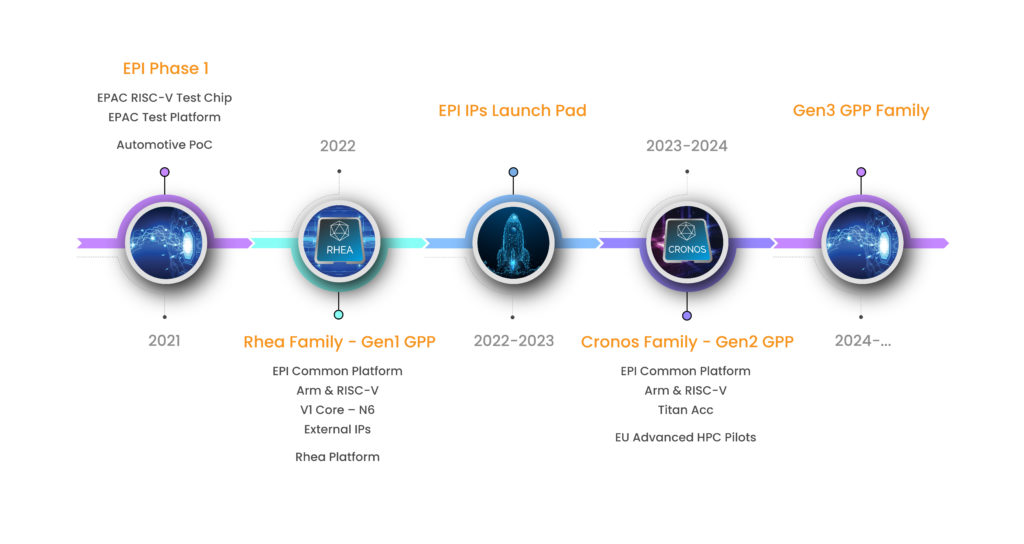

Based on this project progress, the Consortium is ready to announce the updated project roadmap shown below:

European Processor Initiative will, together with colleagues from other European exascale projects, attend the virtual Supercomputing20, where we will showcase our latest developments and update to the roadmap. We invite you to attend our virtual booth and join in the lively discussions about the future of HPC!

At this year’s first virtual Supercomputing 20, the European Processor Initiative has invited several European exascale projects to share our virtual booth and showcase their progress, ideas, and results. Representatives from all of the projects and the European Processor Initiative will be available at our online booth for video chats.

The projects are:

- ASPIDE – https://www.aspide-project.eu/

- DEEPEST – https://www.deep-projects.eu/

- Evolve – https://www.evolve-h2020.eu/

- ExaQUte – http://www.exaqute.eu/

- IDEAS – http://ideas.mango-project.eu/

- LEXIS – https://lexis-project.eu

- MAESTRO – https://www.maestro-data.eu/

- Mont-Blanc 2020 – https://www.montblanc-project.eu/

- SAGE 2 – http://www.sagestorage.eu/

We look forward to your visiting our booth and booking appointments for video chats with any of our representatives!

The schedule for all projects, if you want to catch someone in particular, is here:

November 17th, 2020

- 10 am – 12 pm EST – European Processor Initiative: Mario Kovač (UNIZG-FER), Fabrizio Magugliani (E4)

- 12 pm – 2 pm EST – European Processor Initiative: Andrea Bartolini (UNIBO), Mario Kovač (UNIZG-FER), Jesus Labarta (BSC) – with presentation: “The RISC-V vector processor in EPI”

- 2 pm – 4 pm EST – Mont-Blanc: Pascale Bernier-Bruna (Atos), ExaQUte: Tomáš Karásek (IT4I)

- 4 pm – 5:30 pm EST – EVOLVE: Catarina Pereira (LOBA), Jean-Thomas (DDN), Sage2: Sai Narasimhamurthy (Seagate)

November 18th, 2020

- 10 am – 12 pm EST – European Processor Initiative: João Domingos, Pedro Tomás, Leonel Sousa (IST), Josip Knezovic (UNIZG-FER)

- 12 pm – 2 pm EST – Mont-Blanc: Pascale Bernier-Bruna (Atos)

- 2 pm – 4 pm EST – LEXIS: Jan Martinovič, Kateřina Slaninová, Marc Derquennes, Marc Levrier (IT4I)

- 4 pm – 5:30 pm EST – MAESTRO: Dirk Pleiter (FZJ), European Processor Initiative: Mario Kovač (UNIZG-FER), Fabrizio Magugliani (E4)

November 19th, 2020

- 10 am – 12 pm EST – European Processor Initiative: Daniel Hofman (UNIZG-FER), Fabrizio Magugliani (E4)

- 12 pm – 2 pm EST – LEXIS: Jan Martinovič, Kateřina Slaninová, Marc Derquennes, Marc Levrier (IT4I)

- 1:30 pm – 3 pm EST – DEEP: Jan Schulze (Leibniz Supercomputing Centre), IDEAS: Maxime Bidault (EATON)

This week, on September 23-24, Korea Supercomputing Conference 2020 was held virtually and it hosted many distinguished guests who discussed the Exascale computing era. Jean-Marc Denis, EPI’s Chairman of the Board, was invited as a keynote speaker with a talk titled “The European approach for exascale ages. The road toward sovereignty”.

He explained EPI’s short-term objectives – which is to supply the EU-designed microprocessor to empower the EU exascale machines, and long-term objective, which is that Europe needs independent and sovereign access to high-performance, low-power microprocessors, from IP to products.

EPI’s mission was highlighted and fortified once again, seeing that Mr Denis’ talk came only days after the President of the European Commission, Ursula von der Leyen gave her first State of the Union speech, in which she said Europe will invest 8 billion euros in the next generation of supercomputers – cutting-edge technology made in Europe.

The full presentation is available in our repository: https://www.european-processor-initiative.eu/dissemination-material/epi-ksc20/, while the talk can also be viewed at EPI YouTube channel: https://www.youtube.com/watch?v=giicOMSG0uQ.

President of the European Commission, Ursula von der Leyen in her State of the Union speech on September 16, 2020, announced new steps in the Digital Decade agenda.

The European Commission has proposed a new regulation to help Europe achieve the leading role in supercomputing and quantum computing, and it will enable an investment of €8 billion in the next generation of supercomputers.

Von der Leyen said that the “[N]extGenerationEU is also a unique opportunity to develop a more coherent European approach to connectivity and digital infrastructure deployment. None of this is an end in itself – it is about Europe’s digital sovereignty, on a small and large scale. In this spirit, I am pleased to announce an investment of 8 billion euros in the next generation of supercomputers – cutting-edge technology made in Europe. And we want the European industry to develop our own next-generation microprocessor that will allow us to use the increasing data volumes energy-efficient and securely. This is what Europe’s Digital Decade is all about!”

SOTEU speech can be find here: https://ec.europa.eu/commission/presscorner/detail/en/SPEECH_20_1655

Full press release is here: https://ec.europa.eu/commission/presscorner/detail/en/ip_20_1592

Introduction

The European Processor Initiative (EPI) is building a new central processing unit (CPU) with European technology. This CPU will bundle an accelerator, based on the open source RISC-V architecture. This accelerator will include support for the upcoming V-extension of RISC-V. At the Barcelona Supercomputing Center (BSC), we have been busy at work building software tools and infrastructure to explore and learn about the benefits and challenges that this extension brings to the table.

The RISC-V ISA

RISC-V is a relative newcomer in the Instruction Set Architecture (ISA) space, along with well-established ones like x86-64 and AArch64. Its main distinctive feature is that it is an open source specification that anyone can take to implement and extend, be it for commercial purposes or research studies. The specification is maintained by the RISC-V Foundation and its members.

Another important aspect of the RISC-V ISA is the fact that it has been designed to be modular. Conscious that not all the features present in modern ISAs may be of interest to everyone, the ISA is structured in a base specification and a set of standard extensions. Also, given its open source nature, anyone can define their own non-standard extensions, and the ISA caters to that possibility by providing customization features. Standard extensions have the advantage that they are eventually ratified by the RISC-V Foundation and its members after a collaborative development of the specification and gathering of experience in early implementations.

The V-extension

Standard extensions are commonly identified with a single letter. One of them is the V-extension. V stands for vector. This extension aims to provide vector computation capabilities to the RISC-V ecosystem. It is currently under development so no hardware or software exists that supports it.

Programs running on a computer are made up by a number of instructions. Each instruction is executed by the CPU, and most of them just do a simple operation on a single data value. For instance, an instruction may add two numbers. While this is perfectly reasonable for most applications, there are several domains, spanning from High Performance Computing (HPC) to Digital Signal Processing (DSP), where applications need to repeatedly perform the same computation over a regular set of data. In our running example, rather than just adding two numbers, applications in these domains are better served by an instruction that is able to add, pair-wise, two sets of numbers. These sets of numbers are called vectors (conversely, a single number is called a scalar). In this scenario, using vector instructions can result in applications that run more efficiently both in time and in energy consumption.

These kind of instructions traditionally have been called Single Instruction Multiple Data (SIMD), as a single instruction is able to operate over a set of data instead of individual elements. Many of the well-established vendors like Intel and Arm already provide SIMD instructions in the ISAs they maintain. Examples are Intel’s SSE, AVX-2 and AVX-512 and Arm’s Advanced SIMD and SVE.

There are a number of distinctive features in the V-extension that make it very interesting and also pose some challenges to implementers. An important one is that the extension does not prescribe the length of the vectors. Traditional SIMD ISAs prescribe the size of a vector as 128, 256 or 512 bit. A drawback with this approach is that a new ISA is required every time there is an interest to enlarge the vectors. The alternative is to allow the vendor to choose the size depending on its market needs. For instance, this is what Arm’s SVE does, where vectors can range from 128 bit to 2048 bit, in multiples of 128 bit. The V-extension currently only requires the width to be a power-of-2, so it is possible to cover markets that are well served with shorter vectors, like DSP, and also markets that benefit from longer vectors, like HPC.

Another interesting feature of the V-extension is that it restores the concept of vector length, a feature reminiscent of ancient vector architectures of the 1970s. The vector length tells the CPU how many elements in the vector have to be processed.

SIMD ISAs often process the whole vector so this concept does not exist there. An application has to consider the case when there is not enough data to fill a full vector. One option is to resort in this case to regular, scalar, instructions. Another option is to keep using vector instructions but discard some of the results computed, using a common feature called masking that may come with an extra penalty. The vector length can be used to reduce the number of elements being processed without requiring extra instructions, like in the first option, or having to compute a mask. For some implementations like in EPI’s VPU, shortening the vector length also allows to shorten the latency of instructions – no computation cycle is needed for the unused “tail” of the vector.

Exploration

To explore the software side of the V-extension, we took the LLVM open source compiler which, except for the V-extension, already has good support for a number of the standard extensions of RISC-V. LLVM is an umbrella project for open source compiler and other toolchain-related projects like linkers or static analyzers.

In order to enable the exploration of the V-extension, we designed and implemented an initial set of C/C++ builtins. These builtins allow the C/C++ developers to be able to target the V-extension instructions from their applications. Along with our partners at EPI, we have ported several computational kernels, core parts of applications that are used very frequently, using the developed builtins. Some of those kernels are classic in HPC, such as matrix multiply, sparse matrix vector and the FFTW implementation of the Fast Fourier Transform (FFT). Algorithms from other domains, such as cryptography, have also been evaluated under the V-extension.

Finally, we also implemented in the compiler initial autovectorization support. A compiler can determine that vector instructions can be used without having to use builtins. Because of the two distinctive features of V-ext described earlier, compilers do not have good support yet in this area. Most of our work here is very infrastructural in making sure the compiler can vectorize in the way we believe is the best for the V-extension. We hope to be able to provide better support in this area, which is under intense work-in-progress status.

The V-extension is still being built, so no hardware exists that can execute V-extension instructions. This limits users and developers of the compiler as they would not be able to tell if their program and the compiler work correctly. To unblock this issue, we developed an emulator, called Vehave, that runs on top of existing RISC-V Linux platforms. This way the correctness of the applications and the compiler can be validated using the emulator.

We also implemented in the emulator a mechanism to generate traces of the executed vector instructions. These traces can be loaded in BSC’s trace visualization tool Paraver. This provides information valuable to the users and developer of the compiler.

For instance, application developers can determine that their application requires the compiler instructions that are known to be slow in a specific implementation of the V-extension. Compiler developers can identify redundant instructions or complicated instruction sequences. At BSC, we identified some of those complicated instruction sequences and we reported to the V-extension work group. The specification was extended with new individual instructions that achieve the same functionality of the original sequences.

In order to allow quicker experimentation, since all compilers are large pieces of software, we installed a version of Compiler Explorer that can work with the compiler we developed. This way it is possible to share small snippets of code to evaluate the quality of the code emitted by the compiler. This tool is publicly available at https://repo.hca.bsc.es/epic

The Initiative will gather experts to discuss exascale future on March 16-17, in Paris

The European Processor Initiative is announcing the first EPI Forum to take place in Paris, France, on March 16-17, 2020.

EPI is going full speed ahead to meet the goals of our mission – European independence in HPC technologies and a favorable global position in the race towards exascale.

In a two-day event, the consortium will host experts from HPC ecosystem, engineers, researchers and global players in the field, to attend sessions, round tables and keynote speeches from prominent executives and experts.

Hosted near the beautiful Champs-Élysées, at the Elysées Biarritz venue, the first day of the event will tackle interesting topics such as architecture choice, the rise of EPI Common Platform as an EU central computing unit, an overview of processing cores, and the introduction of SiPearl, EPI’s industrial hand.

The forum will also provide the attendees with inputs and worldwide views from technology providers and intriguing discussion regarding bringing new EU HPC processor to market and associated challenges. Prominent keynotes include experts such as Brent Gorda, senior director of HPC, Infrastructure Line of Business Arm, Steve Scott, SVP, Senior Fellow & CTO of the HPC & AI Business Unit at HPE, Paul de Bot, Senior Director, TSMC Europe B.V., Mitsuhisa Sato, Deputy Director, RIKEN Center for Computational Science, and Robert Hoekstra, PhD, Manager, Scalable Architectures, Computing Research Center, Sandia National Laboratories.

The second day of the EPI Forum will feature a keynote speech from RISC-V Foundation CEO, Calista Redmond, followed by discussions on automotive and edge HPC, EPI software stack, programming models, use of accelerator cores and exascale applications.

“EPI project is strongly supported by the European Commission and we are proud to serve the European ambition toward sovereignty. As sovereignty is becoming more and more important, EPI is going to play a central role in the European HPC landscape. Initially, with the design of the RHEA processor, on next-generation Arm® Neoverse™ architecture, we are going to equip the European exascale supercomputer. In parallel, as part of our long-term strategy, we are starting to build foundations for our future European IP toolbox based on a variety of IP solutions including RISC-V, which will target custom accelerators and microprocessors. Our ambitious vision should begin to show concrete results with first-generation processors by SiPearl in the field by 2022. The first EPI Forum, much like the project itself with its strategy of supplying products in the short term and achieving EU sovereignty in the long term, will allow attendees to become acquainted with how those short- and long-term ambitions are tightly articulated,” stated Jean-Marc Denis, EPI Chairman of the Board.

“There is demand for the type of performance and innovation that Arm Neoverse-based processors deliver, and this is evident in the growth of the Arm HPC ecosystem,” said Chris Bergey, SVP and GM, Infrastructure Line of Business, Arm. “Our collaboration with the EPI and SiPearl is strategically important to our goals in HPC, and Arm supports the EU on its road toward greater processor independence and exascale deployments.”

“As the European number one in High-Performance Computing, Atos is fully supportive of the EuroHPC Joint Undertaking’s ambitious strategy to boost European technological self-reliance. Atos is proud to lead the effort to design a family of European processors for HPC and for other emerging markets, in our role of coordinator of the EPI project. Atos has a long history of commitment to the development of the Arm ecosystem for HPC, particularly through our role in the pioneering Mont-Blanc projects. With EPI, we are taking this ambition to a different scale, and this is good news for the robustness of the European industry,” said Arnaud Bertrand, Senior Vice President, Global Head of BDS Strategy, Innovation and R&D at Atos.

“HPE has been a strong supporter of the Arm ecosystem with both our Apollo and Cray systems and software for HPC and AI and we are excited to partner with SiPearl and the EPI consortium,” said Peter Ungaro, senior vice president and general manager, High-Performance Computing and Mission Critical Solutions, HPE. “As the leader of the global hybrid IT and HPC markets, HPE is uniquely positioned to leverage and distribute SiPearl processors on future systems to customers around the world.”

“The future of computing is dramatically changing, driven by the digitalization of many industries as compute workloads change with the arrival of big data,” said Ravi Subramanian, senior vice-president at Mentor, a Siemens Business. “The European Processor Initiative is the most significant pan-European initiative in computing over the past two decades. Mentor is excited to participate in and contribute to this initiative by bringing key experts together in Paris for the first EPI Forum to help chart the future of the entire EPI ecosystem.”

“As a key partner to the European Processor Initiative, we are proud that our solutions contribute toward the creation of state-of-the-art high-performance computing processor technologies designed in Europe, “ said Luc Elman, VP Customer Excellence Europe at Synopsys.”

“GENCI as a French actor of the HPC-driven and AI-driven simulation activities in science is very proud to participate and support the EPI initiative which will achieve a major contribution to the European sovereign digital revolution supported by co-designed exascale systems funded by EuroHPC,” said Philippe Lavocat, President and CEO of GENCI.

Event details and registration is available at https://www.european-processor-initiative.eu/epi-forum/.

The 20th HiPEAC conference held in Bologna, Italy, from January 20th to 22nd is behind us and it was a special event for the members of the Initiative. In addition to being a sponsor of the conference, with a booth visited by many attendees, EPI members made themselves a busy schedule, participating in sessions on each day of the conference.

On the first day, Imen Baili from Menta, participated in the WRC: Workshop on Reconfigurable Computing, with a presentation titled European Processor and the role of eFPGA, where she spoke about FPGA applications and the difference between Menta’s eFPGA solution VS FPGA. She also addressed the advantages such a solution brings to EPI, offering the most robust verification flow as well as the fact that pure digital IP guarantees very fast delivery.

On the second day of the conference, John Davis, from BSC attended the Eurolab4HPC Industrial Session on Open Source Hardware and introduced LOCA – the European Laboratory for Open Computer Architecture. In his presentation, he also addressed the RISC-V involvement in EPI.

In addition to the sessions and EPI workshops organized, Fabrizio Magugliani from E4 and Andrea Bartolini from the University of Bologna, held a 10-minute industry session introducing EPI and inviting the attendees to attend the EPI Tutorial.

On the very last day, after discussing with many interested attendees and STEM students, EPI team organized our own tutorial titled “First steps towards a made-in-Europe high-performance microprocessor”, covering the latest in EPI.

Josip Knezović, from UNIZG-FER, gave a general introduction into the tutorial, while Denis Dutoit from CEA covered General EPI overview and details of EPI’s Common Platform and Rhea 1st implementation.

Mauro Olivieri from BSC and Andrea Bartolini from UNIBO followed up with two very important aspects as well – accelerators in EPI and EPI power management, while the first section of the tutorial was closed by a presentation from Fabrizio Magugliani from E4 on EPI PCIe daughter card as a software development vehicle. After a short break, BSC’s team members Filippo Mantovani and Roger Ferrer Ibáñez closed the tutorial with a session on Bringing up EPI RISC-V Vector architecture Software, with a demonstration on software-emulated vector instruction explorations for RISC-V-based accelerator.

Materials and presentations from EPI’s sessions are available in our Dissemination repository:

SiPearl, EPI’s industrial and business hand, joins the EPI consortium as its 27th partner and moves into its operational phase.

SiPearl and its solutions will help drive the development of the European market for high-performance computing (HPC), as well as its strategic applications such as artificial

intelligence and connected mobility. SiPearl will develop and market its solutions through close collaboration with its 26 partners from the EPI – scientific community, supercomputing centers and leading names from the IT, electronics and automotive sectors – which are its stakeholders and future clients.

Read the full press release here: https://www.sipearl.com/press/PR_SiPearl_launching_21012020.pdf and visit the company website here: https://www.sipearl.com/.