The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 30 partners from 10 European countries, aiming to make the EU independent in HPC chip technologies and HPC infrastructures, is proud to announce that it has delivered a significant European sovereignty contribution with valuable business impacts.

One of its key partners, Eviden, the Atos Group business leading in advanced computing, as part of a consortium together with ParTec, the German modular supercomputing company, have won an emblematic contract with EuroHPC to provide the very first Exascale supercomputer in Europe, named JUPITER. SiPearl, another key EPI partner, will provide its brand new Rhea1 processor, an outcome of the EPI initiative [1], the first HPC-dedicated European processor on the market with exceptionally high memory bandwidth. JUPITER is a EuroHPC JU supercomputing infrastructure that will be operated by Forschungszentrum Jülich in Germany. This is a major milestone for SiPearl and EPI in fulfilling the European Union’s mission to ensure European sovereignty through the return of high-performance, low-power processor technologies in Europe. It will contribute to the development of high-precision models of complex systems and artificial intelligence applications to solve strategic, scientific, industrial and environmental challenges with a low-carbon footprint.

JUPITER will be composed of two partitions, a highly scalable GPU accelerated Booster Module and a general-purpose Cluster Module with high memory bandwidth processors. The general-purpose Cluster Module will be based on SiPearl’s first-generation processor, Rhea1. Using the Arm® NeoverseTM V1 platform, the Rhea1 is characterized by very high memory bandwidth, extraordinary compute performance and efficiency for an unmatched Byte/Flop ratio. It will help JUPITER run complex simulations and artificial intelligence applications to solve strategic, scientific, industrial and environmental challenges with a low-carbon footprint. Rhea1 will be available in 2024.

“I am proud of this outstanding achievement, and I value the EPI team’s cooperation. Together we are paving the way towards Europe’s technological sovereignty. This is creating an unprecedented momentum for EPI to deliver its promises: European processors and accelerators for European exascale supercomputers. EPI is committed to supporting Eviden, Jülich, and SiPearl, key members of EPI, as well as Partec that is close to us, to make JUPITER a great European success” – said Eric Monchalin, Chairman of the EPI Board.

“JUPITER’s dynamic modular architecture will demonstrate the benefits of using different processor types such as CPUs and GPUs in dedicated compute modules. We are excited about the power saving and execution speed opportunities that SiPearl’s unique Rhea processor with its high memory bandwidth, a brainchild of EPI, will open up for JUPITER” – highlighted Prof. Thomas Lippert, Director of the JSC, Forschungszentrum Jülich.

“SiPearl is pleased to take part in this very first European exascale supercomputer. This is a great achievement for us and we look forward to working hand-in-hand with Jülich, Eviden and ParTec, our partners from the EuroHPC ecosystem. The dream of a European machine crossing the exaflop threshold with a European processor inside is coming true”, concluded Philippe Notton, CEO and founder of SiPearl.

“We are extremely proud to be providing our BullSequana XH3000 for the first Exascale supercomputer in Europe and to be supporting our economic and industrial sovereignty. This powerful system will enable new breakthroughs in key sectors, such as medicine and climate change, and stimulate innovation for the whole European scientific community.” said Emmanuel Le Roux, Group SVP, Global Head of HPC, AI & Quantum at Eviden, Atos Group.

“Developing a strong European HPC supply chain with energy-efficient components and technologies is key to achieving digital sovereignty in Europe while promoting more sustainable supercomputing. The fact that a European microprocessor will underpin the first European supercomputer to exceed the one exaflop threshold is a pivotal victory for Europe!” said Anders Dam Jensen, Executive Director of the EuroHPC Joint Undertaking.

About EPI

The European Processor Initiative (EPI) is a project whose aim is to design and implement a roadmap for a new family of European low-power processors for extreme scale computing, high-performance Big-Data and a range of emerging applications.

The project has received funding from the European High Performance Computing Joint Undertaking (JU) under Framework Partnership Agreement No 800928 and Specific Grant Agreement No 101036168 (EPI SGA2). The JU receives support from the European Union’s Horizon 2020 research and innovation programme and from Croatia, France, Germany, Greece, Italy, the Netherlands, Portugal, Spain, Sweden, and Switzerland.

The European High Performance Computing Joint Undertaking (EuroHPC JU) has launched 3 new research and innovation projects. The projects aim to bring the EU and its partners in the EuroHPC JU closer to developing independent microprocessor and HPC technology and advance a sovereign European HPC ecosystem. The European Processor Initiative (EPI SGA2), The European PILOT and the European Pilot for Exascale (EUPEX) are interlinked projects and an important milestone towards a more autonomous European supply chain for digital technologies and specifically HPC.

With joint investments of €140 million from the European Union (EU) and the EuroHPC JU Participating States, the three projects will carry out research and innovation activities to contribute to the overarching goal of securing European autonomy and sovereignty in HPC components and technologies, especially in anticipation of the European exascale supercomputers.

The three projects have been selected following two calls for proposals: H2020-JTI-EuroHPC-2020-01 for EUPEX and The European PILOT, and H2020-JTI-EuroHPC-2020-02 for EPI SGA2.

Anders Dam Jensen, the European High Performance Computing Joint Undertaking (EuroHPC JU) Executive Director, said:

“Developing a strong European HPC supply chain with independent components and technologies is key to achieve strategic autonomy and digital sovereignty in Europe. The three projects, EPI 2, EUPEX and The European PILOT are critical to make successful our transition towards exascale while developing a world-class, competitive and innovative supercomputing ecosystem across Europe.”

“The EPI consortium brings together the best industrial and academic expertise in Europe: it combines the best of both worlds, academic innovation with industrial strength. We are thrilled to be given the opportunity to build on the momentum generated by phase 1 of the project and continue to develop the technologies that will power future European exascale systems. We look forward to seeing our components (processors & accelerators) experimented and used – in pilot projects and beyond.” said Etienne Walter, Atos, the EPI Phase 2 General Manager.

“All members of the EUPEX consortium are extremely proud to participate in this pilot for exascale, a project on an unprecedented scale, which is the culmination of more than 10 years of European HPC research and development towards exascale supercomputing. EUPEX will crystallize the research efforts of many projects – from Mont-Blanc projects to DEEP projects – and validate EPI processors with all these European technologies within the framework of a coherent but modular pilot platform. EUPEX will pave the way for a self-reliant European HPC industry, capable of delivering exascale-class supercomputers manufactured in Europe.” said Jean-Robert Bacou, Atos, the EUPEX coordinator.

“The European Pilot project will contribute to a sustainable exascale HPC in Europe and it will help build the groundwork for long-term technical independence. Hardware wise, The European Pilot leverages and significantly scales up EPI advancements built from scratch, such as EPAC, in the form of massively parallel arrangement of HPC vector and machine learning accelerators. These European-IP accelerators and customized software ecosystem will deliver near-exascale levels of performance at unparalleled levels of scale of integration. The European Pilot systems will be deployed in liquid immersion cooling tanks supporting ultra-efficient power densities. The know-how to build these supercomputers will help establish digital autonomy within the EU” said Carlos Puchol, Barcelona Supercomputing Center (BSC), the European Pilot coordinator.

European Processor Initiative (EPI)

The consortium of the European Processor Initiative (EPI) started the second implementation phase of the initiative on 1 January 2022. The project is implemented under the framework partnership agreement in European low-power microprocessor technologies which focuses on microprocessor technologies to develop competitive European technology for HPC and other applications.

Central goals of the initiative are:

- Strengthening the competitiveness and leadership of European industry and science;

- Developing European microprocessor technology with drastically better performance and power ratios;

- Tackling important segments of broader and/or emerging HPC and Big-Data markets.

The second implementation phase of the EPI will continue the initial developments of the phase 1 on a European microprocessor and accelerator to support European technological autonomy and sovereignty in this critical area. Based on a solid, long-term economic approach, the EPI will deliver central components of future European supercomputers to boost innovation and the digital transformation of the European economy.

The specific focus of the second phase is to finalise the development of the first generation of low-power microprocessor units and accelerators, enhancing existing technologies to target the incoming European Exascale machines, develop the second generation of and ensuring paths for industrialisation and commercialisation of these technologies.

The microprocessors units are leveraging on Arm architecture, and the accelerators on Risc-V instruction set architecture. The EPI has established close links to two pilots towards the European exascale supercomputers where the developed technology will be demonstrated and made available for software development.

The project is coordinated by Atos (Bull SAS). It will run for 3 years with a budget of up to €70 million provided by the EU and the Participating States of the EuroHPC JU.

European Pilot for Exascale (EUPEX)

EUPEX was launched on 1st January 2022 and will develop the first European platform for HPC, gathering and integrating the full breadth of European technologies, from system architecture, processor, system software and development tools, all the way to applications. The EUPEX platform will be a production-grade prototype designed to be open and scalable, and leveraging the HPC technologies used and developed by its scientific and industrial partners. The pilot system will also serve as a development vehicle for software and applications in collaboration with European key user communities.

EUPEX aims to directly support an emerging and vibrant European entrepreneurial ecosystem around European HPC technology, addressing related sectors such as Artificial Intelligence (AI) and Big Data processing. It will be a vehicle to prepare communities working in HPC, AI and Big Data for the upcoming European Exascale systems and federated HPC infrastructure.

The project is coordinated by Atos (Bull SAS). It will run for 4 years with a budget of up to €40.7 million provided by the EU and the Participating States of the EuroHPC JU. EUPEX is linked to The European PILOT through a collaboration agreement to ensure an aligned evolution of European technology towards the next generation of supercomputers.

Pilot using Independent, Local and Open Technologies (The European PILOT)

From 1 December 2021, The European PILOT project (Pilot using Independent, Local and Open Technologies) started working on designing a European accelerator leveraging and extending developments within the framework partnership agreement in European low-power microprocessor technologies.

Accelerators typically provide most of the nominal floating-point performance in modern HPC systems and represent fundamental building blocks of current and future Exascale HPC systems. The European PILOT will demonstrate an accelerator on the basis of European technology and an open standard using the RISC-V instruction set architecture. The integration of accelerators into a highly dense pilot HPC system with liquid immersion cooling technologies will be an important contribution to the European HPC ecosystem.

The project is coordinated by the Barcelona Supercomputing Center (BSC) and brings together multiple partners to combine existing intellectual property with novel innovation as building blocks for future HPC systems. The project will run for a period of 42 months with a budget of up to €30 million provided by the EU and the Participating States of the EuroHPC JU. The European PILOT is linked to EUPEX through a collaboration agreement to ensure an aligned evolution of European technology towards the next generation of supercomputers.

About the EuroHPC JU

The EuroHPC JU was created in 2018 and recently reviewed by means of Regulation Council Regulation (EU) 2021/1173. 30 European countries are currently taking part in the initiative and pooling their resources with the EU and private partners to enable the EU to become a world leader in supercomputing.

The mission of the EuroHPC JU is to develop, deploy, extend and maintain an integrated world-class supercomputing and data infrastructure in the EU and to develop and support a highly competitive and innovative HPC ecosystem.

On July 19th, the Council Regulation establishing the European High-Performance Computing Joint Undertaking was published in the Official Journal of the European Union. It was formally adopted on July 13th, by the Economic and Financial Affairs Council.

This is an important piece of news for the HPC community, opening up EuroHPC JU’s ability to draw funds from the Horizon Europe, Digital Europe and the Connecting Europe Facility programmes. The news item and full regulation text can be found on the EuroHPC JU’s website, here:

General Assembly of European Processor Initiative has selected a new Chairman of the Board in July. Eric Monchalin from Atos, the company that coordinates the EPI project, is going to lead 28 partners from 10 countries in their efforts to design and implement a roadmap for a new family of low-power European processors.

Eric is experienced in leading 100+ people organizations and managing multi tens millions of Euros projects in international environments. He is a technology-minded person who values wide range of skills and technological knowledge focused on customer expectations to turn them into reality. Furthermore, Eric’s career has been mainly built on numerous Hardware and Software R&D positions in several companies and various domains like signal processing, embedded systems, communication, storage, High Performance Computing and Artificial Intelligence.

Taking place on 30 August – 3 September 2021, the second ACM Europe Summer School on HPC Computer Architectures for AI and Dedicated Applications will be co-hosted by Barcelona Supercomputing Center (BSC), in conjunction with the Universitat Politècnica de Catalunya – Barcelona Tech (UPC).

The programme of this year’s summer school, which will be fully remote, centres around topics within the European Processor Initiative. Open hardware expert Luca Benini (ETH Zürich / University of Bologna) will be discussing machine learning from a RISC-V platform perspective, while the EPI Accelerator stream leader Jesús Labarta (BSC) will train attendees in performance analysis and hybrid programming, helping them get the very best out of their code. Meanwhile, Mauro Olivieri (Sapienza – University of Rome / BSC) will present vector acceleration in high-performance computing (HPC) and edge devices.

Keynote talks will be given by celebrated computer scientists and engineers including Luca Cardelli (Oxford University), Bill Dally (Stanford University / NVIDIA), Mihaela van der Schaar (Cambridge University) and Mateo Valero (BSC). There will also be invited talks by EPI researchers Roger Espasa (Semidynamics) on the RISC-V Avispado core, John Davis (BSC) on building an open-source ecosystem for HPC, and Marc Casas (BSC) on accelerating deep neural network training.

The school chairpersons are Mateo Valero and Josep Fernandez (UPC), while the local organizing committee is led by Eduard Ayguadé, (BSC and UPC), and Fabrizio Gagliardi (BSC and ACM).

“EPI is revolutionising computer architecture to pave the way for Europe’s technological sovereignty. As part of the EPI training programme, this summer school provides the ideal introduction to some of the initiative’s main themes,” commented Jean-Marc Denis (Atos / SiPearl), chairman of the EPI board.

Upon completion of the school, all attendees will receive a certificate and a complimentary ACM student membership. Based on the scores obtained in the practical exercises, the best performing students will receive a certificate of honour and will also invited to interviews with industry sponsors, with a view to a possible internship.

The school includes a poster session, with a prize for the best poster.

Registration will be open until 15 July, and accepted candidates will be informed by 1 August.

To register, complete the registration form on the ACM Europe website.

The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 28 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies is proud to announce that we have successfully booted Linux on our EPAC 1.0 core subset implemented on FPGA.

One key segment of EPI activities is to develop and demonstrate fully European processor IPs based on the RISC-V Instruction Set Architecture, providing power efficient and high throughput accelerator core named EPAC (European Processor Accelerator). Using RISC-V will allow leveraging open-source resources at hardware architecture level and software level, as well as ensuring independence from non-European patented computing technologies.

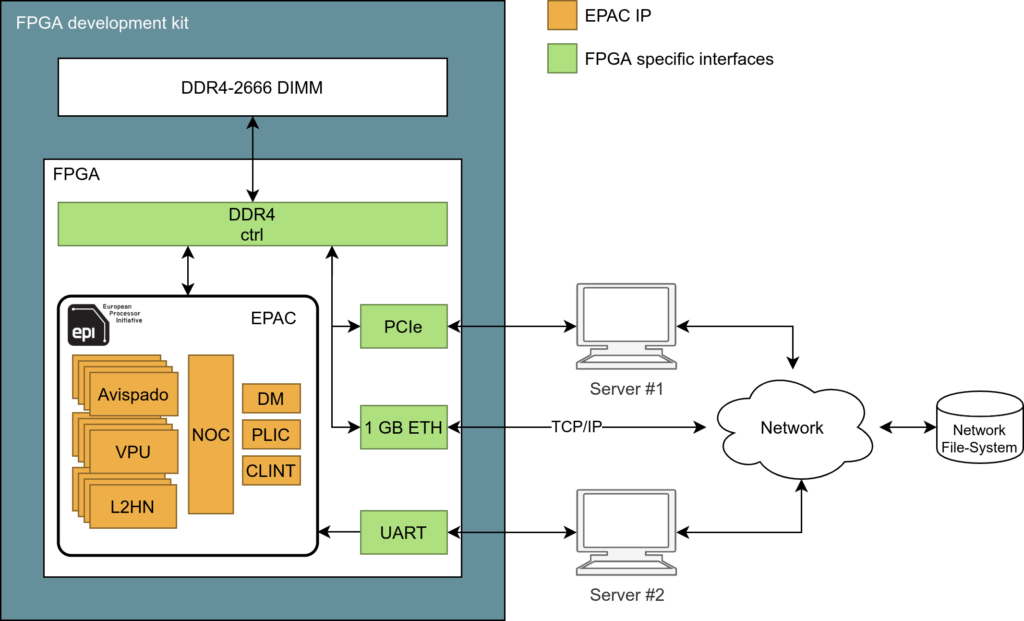

First silicon implementation of EPAC 1.0 test chip is expected in the second half of 2021 and as an important technical milestone towards that goal, we have successfully booted Linux on a subset of EPAC 1.0 synthesized on FPGA. The FPGA design includes the Avispado RISC-V core, the Vector Processing Unit (VPU), the Network on Chip (NoC), the Shared L2 Cache with Coherence Home Node (L2HN), interrupt controllers, IO peripherals and several other components. This implementation will enormously speed-up software development on the EPI HPC architecture as well as testing and improving the architecture for next generations EPAC chips.

For the development of the EPI Accelerator Test Chip, we make extensive use of FPGA technologies to verify the RTL design of the Test Chip. The subset of EPAC 1.0 emulated on FPGA we use as Software Development Vehicle (SDV) to enable early software development before the actual Test Chip silicon comes back from the foundry.

The use of FPGAs enables the testing of RTL blocks with real and very complex software in timescales that are not tractable using pure RTL simulation. Also, it allowed us to stress memory coherence and several related corner cases. We have managed to boot Linux using the EPAC 1.0 system on FPGA and the system boots within a few dozens of seconds compared to weeks using pure simulation. The system is fully usable and interactive for system software and application development and it also includes Ethernet connectivity to enable running large and complex software packages, e.g., OpenMP, MPI.

This is a serious proof of concept that gives us the confidence of a functional and viable future product.

More details on the results can also be found on EPI YouTube Channel, where you can find the second episode of EPI Talks podcast, themed with booting Linux:

Channel: https://www.youtube.com/c/EuropeanProcessorInitiative/featured

Video: https://www.youtube.com/watch?v=X4klPnBjstI

This year’s HiPEAC conference was supposed to be held in beautiful Budapest, from January 18th to 20th 2021. However, due to the persistent pandemic conditions, it had to be moved to a digital edition.

European Processor Initiative’s consortium gladly accepted the opportunity to participate, both as a sponsor and with a tutorial given to the attendees. Our tutorial was held on Monday, January 18th, and it involved the following topics and presenters:

- Denis Dutoit, CEA: EPI overview and introduction to tutorial topics

- Sergio Saponara, UNIPI: Hardware security module in the EPI GPP

- Fabrizio Magugliani, E4: Update of the PCIe boards as development testbed for EPI

- Lilia Zaourar, Tanguy Sassolas, CEA: SESAM/VPSim: fast and highly configurable simulation framework for the EPI processor

- Andrea Bartolini, Giovanni Bambini, UNIBO: Emulating the power controller of the HPC power management systems

The tutorial was very well attended, and the attendees had a lot of interesting questions.

In addition to the tutorial, the EPI team has also hosted a virtual Brazen booth, where students, young researchers, and other prospective employees popped in to ask questions about the project. From the industrial side of EPI, Fabrizio Magugliani presented EPI in the industrial session, while Jurgen Becker attended the WRC workshop and gave an invited talk that involved EPI as well.

All of the presentations from HiPEAC given by EPI members can be found in our repository:

https://www.european-processor-initiative.eu/dissemination-material/epi-at-hipeac-2021/, while the tutorial video is also available on our YouTube Channel: https://www.youtube.com/watch?v=4AYDc6THtcM&t=9476s.

Finally, a shout-out to organizers: even though the team is more than eager to participate in the next one, hopefully live, HiPEAC conference, we are thankful to organizers for such a wonderful experience and the opportunity to share our views and ideas.

The European Processor Initiative, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is finishing its second year of activities.

Despite 2020 bringing upon our young efforts the circumstances that were previously unimaginable, causing the subsequent cancellation of the first-ever planned European Processor Initiative Forum, the partners in the Initiative managed to stay the course and maintain all activities in all designated streams.

The year began with our latest partner, SiPearl, launching to start their activities dedicated to developing commercialized implementations of our technology. Very soon after announcing their presence on the global stage, SiPearl signed a licensing agreement with Arm and opened a branch in Germany.

At the same time, European Processor Initiative partners have finalized the first version of our RISC-V accelerator architecture, named EPAC, and we look forward to the delivery of the first European Processor Initiative silicon featuring EPAC Test Chip in the exciting year that follows. The EPAC Test Chip silicon will be complemented with PCIe EPAC Test Platform enabling the test and enhancements of the architecture for future revisions.

At the software level, we already have a compiler supporting RISC-V vector intrinsics and automatic parallelization of C/C++ codes. We are evaluating the generated code on emulation platforms that provide detailed insight for the holistic co-design of applications, compiler, and architecture. We also have other software development vehicles (SDV) where we are adapting the Operating System for the Heterogeneous ARM+RISC-V architecture of the European Processor Initiative project.

Our automotive activities in the previous year have been focused on the design of state-of-the-art automotive high-performance computing proof-of-concept with the ambition to demonstrate how European Processor Initiative IP will enable future ADAS functionality, paving the way to exploit the GPP, the RISC-V platform, the Kalray MPPA, and the Menta eFPGA IP.

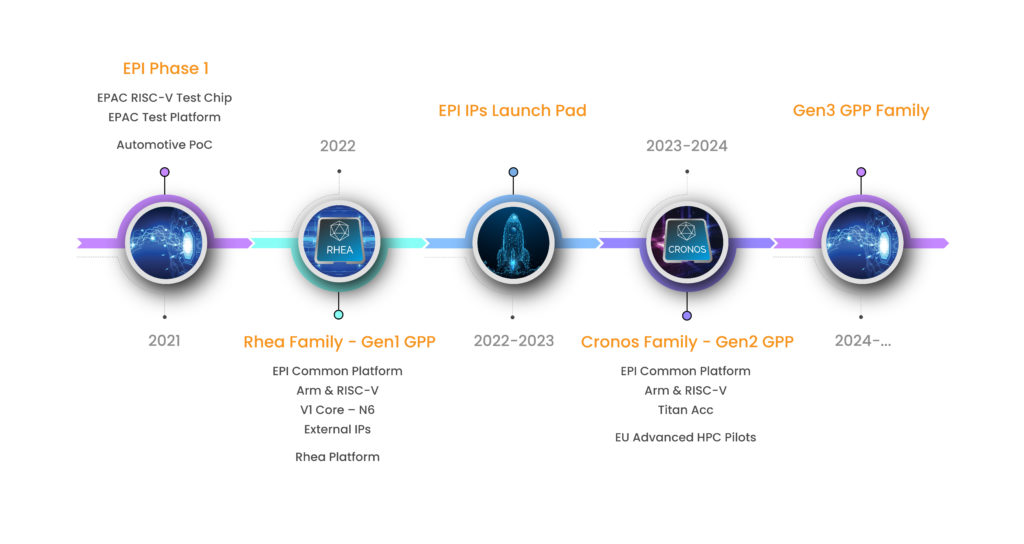

Based on this project progress, the Consortium is ready to announce the updated project roadmap shown below:

European Processor Initiative will, together with colleagues from other European exascale projects, attend the virtual Supercomputing20, where we will showcase our latest developments and update to the roadmap. We invite you to attend our virtual booth and join in the lively discussions about the future of HPC!

At this year’s first virtual Supercomputing 20, the European Processor Initiative has invited several European exascale projects to share our virtual booth and showcase their progress, ideas, and results. Representatives from all of the projects and the European Processor Initiative will be available at our online booth for video chats.

The projects are:

- ASPIDE – https://www.aspide-project.eu/

- DEEPEST – https://www.deep-projects.eu/

- Evolve – https://www.evolve-h2020.eu/

- ExaQUte – http://www.exaqute.eu/

- IDEAS – http://ideas.mango-project.eu/

- LEXIS – https://lexis-project.eu

- MAESTRO – https://www.maestro-data.eu/

- Mont-Blanc 2020 – https://www.montblanc-project.eu/

- SAGE 2 – http://www.sagestorage.eu/

We look forward to your visiting our booth and booking appointments for video chats with any of our representatives!

The schedule for all projects, if you want to catch someone in particular, is here:

November 17th, 2020

- 10 am – 12 pm EST – European Processor Initiative: Mario Kovač (UNIZG-FER), Fabrizio Magugliani (E4)

- 12 pm – 2 pm EST – European Processor Initiative: Andrea Bartolini (UNIBO), Mario Kovač (UNIZG-FER), Jesus Labarta (BSC) – with presentation: “The RISC-V vector processor in EPI”

- 2 pm – 4 pm EST – Mont-Blanc: Pascale Bernier-Bruna (Atos), ExaQUte: Tomáš Karásek (IT4I)

- 4 pm – 5:30 pm EST – EVOLVE: Catarina Pereira (LOBA), Jean-Thomas (DDN), Sage2: Sai Narasimhamurthy (Seagate)

November 18th, 2020

- 10 am – 12 pm EST – European Processor Initiative: João Domingos, Pedro Tomás, Leonel Sousa (IST), Josip Knezovic (UNIZG-FER)

- 12 pm – 2 pm EST – Mont-Blanc: Pascale Bernier-Bruna (Atos)

- 2 pm – 4 pm EST – LEXIS: Jan Martinovič, Kateřina Slaninová, Marc Derquennes, Marc Levrier (IT4I)

- 4 pm – 5:30 pm EST – MAESTRO: Dirk Pleiter (FZJ), European Processor Initiative: Mario Kovač (UNIZG-FER), Fabrizio Magugliani (E4)

November 19th, 2020

- 10 am – 12 pm EST – European Processor Initiative: Daniel Hofman (UNIZG-FER), Fabrizio Magugliani (E4)

- 12 pm – 2 pm EST – LEXIS: Jan Martinovič, Kateřina Slaninová, Marc Derquennes, Marc Levrier (IT4I)

- 1:30 pm – 3 pm EST – DEEP: Jan Schulze (Leibniz Supercomputing Centre), IDEAS: Maxime Bidault (EATON)

This week, on September 23-24, Korea Supercomputing Conference 2020 was held virtually and it hosted many distinguished guests who discussed the Exascale computing era. Jean-Marc Denis, EPI’s Chairman of the Board, was invited as a keynote speaker with a talk titled “The European approach for exascale ages. The road toward sovereignty”.

He explained EPI’s short-term objectives – which is to supply the EU-designed microprocessor to empower the EU exascale machines, and long-term objective, which is that Europe needs independent and sovereign access to high-performance, low-power microprocessors, from IP to products.

EPI’s mission was highlighted and fortified once again, seeing that Mr Denis’ talk came only days after the President of the European Commission, Ursula von der Leyen gave her first State of the Union speech, in which she said Europe will invest 8 billion euros in the next generation of supercomputers – cutting-edge technology made in Europe.

The full presentation is available in our repository: https://www.european-processor-initiative.eu/dissemination-material/epi-ksc20/, while the talk can also be viewed at EPI YouTube channel: https://www.youtube.com/watch?v=giicOMSG0uQ.