The 20th HiPEAC conference held in Bologna, Italy, from January 20th to 22nd is behind us and it was a special event for the members of the Initiative. In addition to being a sponsor of the conference, with a booth visited by many attendees, EPI members made themselves a busy schedule, participating in sessions on each day of the conference.

On the first day, Imen Baili from Menta, participated in the WRC: Workshop on Reconfigurable Computing, with a presentation titled European Processor and the role of eFPGA, where she spoke about FPGA applications and the difference between Menta’s eFPGA solution VS FPGA. She also addressed the advantages such a solution brings to EPI, offering the most robust verification flow as well as the fact that pure digital IP guarantees very fast delivery.

On the second day of the conference, John Davis, from BSC attended the Eurolab4HPC Industrial Session on Open Source Hardware and introduced LOCA – the European Laboratory for Open Computer Architecture. In his presentation, he also addressed the RISC-V involvement in EPI.

In addition to the sessions and EPI workshops organized, Fabrizio Magugliani from E4 and Andrea Bartolini from the University of Bologna, held a 10-minute industry session introducing EPI and inviting the attendees to attend the EPI Tutorial.

On the very last day, after discussing with many interested attendees and STEM students, EPI team organized our own tutorial titled “First steps towards a made-in-Europe high-performance microprocessor”, covering the latest in EPI.

Josip Knezović, from UNIZG-FER, gave a general introduction into the tutorial, while Denis Dutoit from CEA covered General EPI overview and details of EPI’s Common Platform and Rhea 1st implementation.

Mauro Olivieri from BSC and Andrea Bartolini from UNIBO followed up with two very important aspects as well – accelerators in EPI and EPI power management, while the first section of the tutorial was closed by a presentation from Fabrizio Magugliani from E4 on EPI PCIe daughter card as a software development vehicle. After a short break, BSC’s team members Filippo Mantovani and Roger Ferrer Ibáñez closed the tutorial with a session on Bringing up EPI RISC-V Vector architecture Software, with a demonstration on software-emulated vector instruction explorations for RISC-V-based accelerator.

Materials and presentations from EPI’s sessions are available in our Dissemination repository:

SiPearl, EPI’s industrial and business hand, joins the EPI consortium as its 27th partner and moves into its operational phase.

SiPearl and its solutions will help drive the development of the European market for high-performance computing (HPC), as well as its strategic applications such as artificial

intelligence and connected mobility. SiPearl will develop and market its solutions through close collaboration with its 26 partners from the EPI – scientific community, supercomputing centers and leading names from the IT, electronics and automotive sectors – which are its stakeholders and future clients.

Read the full press release here: https://www.sipearl.com/press/PR_SiPearl_launching_21012020.pdf and visit the company website here: https://www.sipearl.com/.

The project is finishing its first year with introduction of a new EPI Common Platform, an updated roadmap and presence at key events

The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 27 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC technologies, is approaching the closure of the first year in its three-year cycle.

During that time, the consortium has submitted several architectural designs to the European Commission and is now ready to show its updated roadmap to the public.

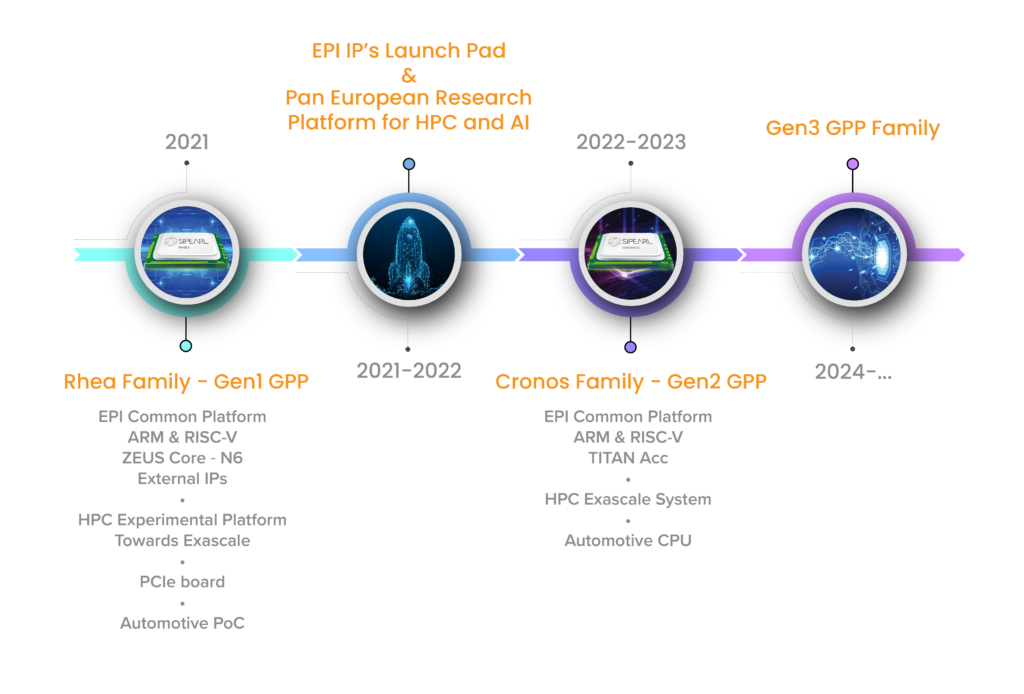

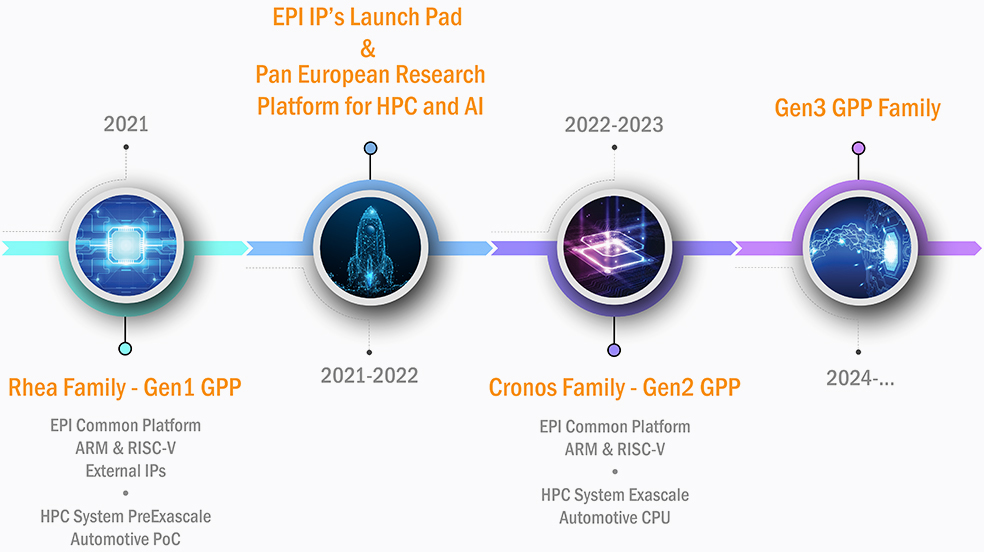

Figure 1. EPI Roadmap

The first-generation chip family, named Rhea, will include Arm ZEUS architecture general purpose cores and prototypes of high energy-efficient accelerator tiles: RISC-V based (EPAC), Multi-Purpose Processing Array (MPPA), embedded FPGA (eFPGA) and cryptography HW engine. First Rhea chips will be fabricated in N6 technology aiming at the highest processing capabilities and energy efficiency.

The Rhea chips will be integrated into test platforms, both in workstations and supercomputers in order to validate the hardware units, develop the necessary software interfaces, and run applications. Rhea aims to be the European processor for several experimental platforms towards exascale HPC and future automotive designs.

Today we also announce our long-term commitment to our recently introduced initiative to harmonize the heterogeneous computing environment by defining a common approach: the EPI Common Platform (CP). The EPI CP is in early development but will include the global architecture specification (hardware and software), common design methodology, and global approach for power management and security, in the future.

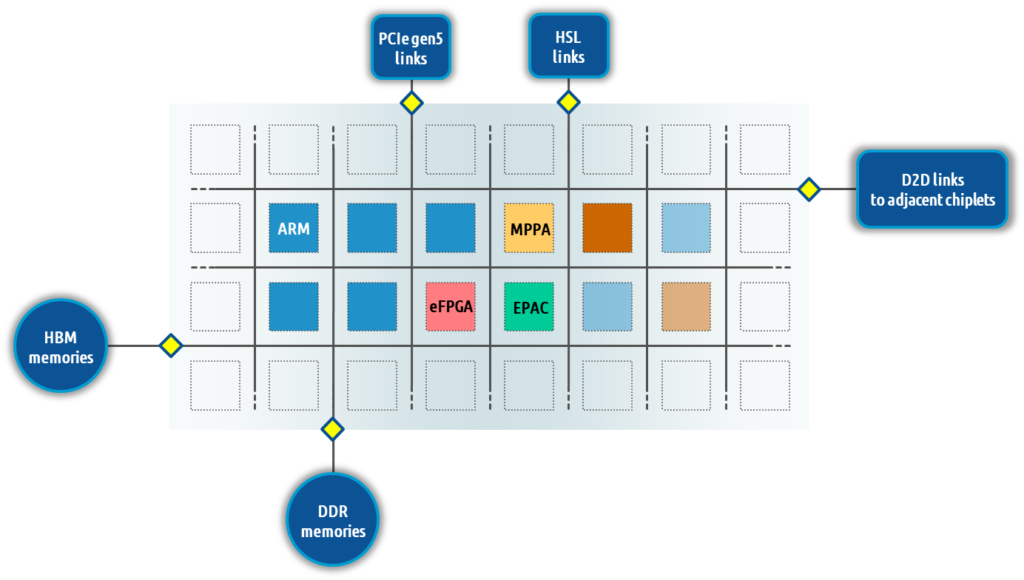

The CP in the Rhea family of processors will be organized around a 2D-mesh Network-on-Chip (NoC) connecting computing tiles based on general purpose Arm cores with previously mentioned accelerator tiles.

Figure 2. EPI Common Platform

A common software environment between heterogeneous computing tiles will harmonize the system, acting as a common backbone of IP components for IO connection with the external environment such as memories and interconnected or loosely coupled accelerators.

With this CP approach, EPI will provide an environment that can seamlessly integrate any computing tile. The right balance of computing resources matching the application needs will be defined through the carefully designed ratio of the accelerator and general-purpose tiles.

These important developments and more will all be presented at high-profile events the Initiative is attending, announced on EPI’s web: https://www.european-processor-initiative.eu/events/.

We invite all interested parties to visit our exhibition booths at upcoming events, with special focus on the Supercomputing Conference in Denver, USA (Nov 17-22, 2019), booth #895, and the European Forum for Electronic Components and Systems in Helsinki, Finland (Nov 19-21, 2019).

Meet us there to discuss EPI’s future!

October started pretty busy for EPI partners, who attended various events presenting the latest from the Initiative.

The calendar was launched by members of Atos and CEA attending the RISC-V Week in Paris, which encompassed two major groups: The 2nd RISC-V Meetings, organized by IRT Nanoelec and CEA and The Scientific Day of IRT SE & GDR SOC2: RISC-V for critical embedded systems, organized by IRT St-Exupéry and GDR SOC2.

Romain Dolbeau from Atos gave a talk titled “European Processor Initiative: challenges & opportunities for RISC-V accelerators in an HPC platform”. He described the currently anticipated architecture of the EPI design and how to leverage this architecture in the software, using open standards. In particular, he touched upon how the EPI project is developing IP for a set of RISC-V-based accelerators designed to connect directly to the processor network-on-chip. He also discussed EPI plans to integrate those IPs in a silicon device, and how other accelerators IP designers could leverage EPI to create new high-performance multi-chip processing devices.

At that same event, Denis Dutoit from CEA gave a talk titled “European Processor Initiative: First step towards a made-in-Europe high-performance microprocessor”. After an introduction on High Performance Computing new challenges and associated technology/architecture evolution, the presentation highlighted the EPI position statement on generic computing, accelerator with RISC-V and design methodology. The presentation concluded with an explanation of EPI’s roadmap towards a wide range of applications from Exascale computing to embedded HPC.

Italian partners also had a very busy week presenting EPI in several workshops and distinguished lectures. Fabrizio Magugliani from E4 Computer Engineering presented at the workshop “Edge computing: Quando il Cloud è troppo lontano”, which confirmed the need for integrating the different streams of data (coming from IoT, the Edge, Industry 4.0 and similar sources) in a consistent view, including the pre-processing of data at the Edge and a HPC-powered analysis in a centralized facility, applying AI and HPDA techniques to the streams and then storing and capitalizing on the ‘knowledge’ extracted from the data. He introduced the roadmap and goals of the EPI and highlighted that the roadmap is fully consistent with the computational need of such a chain of processing.

Only two days later, he also presented at the 12th International Conference on Internet and Distributed Computing Systems in Naples. The speakers listed in the rich agenda detailed how the rapidly evolving technology for Distributed Computing Systems enables to use more computation and ‘intelligence’ at the Edge, and how to maximize the effectiveness of different architectures and components. While these components are ideal for analyzing data at the Edge, more elaborate analysis demands the use of more powerful systems. Having the same Instruction set at the Edge (running Arm devices) as well as in the centralized computing facility is definitely a value, making the EPI processor ideal for seamless integration of the data streams with the EPI-powered centralized facility.

Coming from EPI’s academic wing, University of Pisa’s Prof. Sergio Saponara was invited to give a lecture at the IEEE I&M France Chapter/GDR SoC2 Workshop. He held an IEEE IMS DL about ACES (autonomous, connected, electrified and shared) vehicles and related instruments and measurement/perception tools. The IEEE DL presented the opportunities and challenges of the ACES trends, with a focus on high-performance machine-perception sensors (like Radar, Lidar, Camera), navigation and positioning technologies (Inertial Measurement Units, Global Position/Navigation Satellite Systems). The challenge of the High-Performance Computing, needed on-board the vehicles to process in real-time such large amount of data, using either deterministic signal and data processing techniques or new machine learning and AI tools, have been also discussed. To this aim, the opportunities offered by EPI have been also presented.

Addressing the HPC user community, EPI Chair of the Board, Jean-Marc Denis, attended two HPC User Forums this week – the first in Lugano, Switzerland, and the second in Edinburgh, Scotland, where he presented the road so far, the latest developments and the Initiative future steps.

Across the ocean, another EPI industrial partner, Menta, attended the Arm TechCon in San Jose, California with their exhibition space at which they offered EPI materials for the interested attendees.

The automotive segment of EPI also had a busy week. Karlsruhe Institute of Technology held the first automotive summit in cooperation with the Tongji University in Shanghai. Many representatives from research and companies in China such as BMW, Infineon, Intron and UAES (Bosch in China) participated and gave interesting presentations about their current and future R&D projects. One major topic was autonomous driving and how it can be accomplished with the currently available computing resources, also with solutions ranging from edge and cloud computing to embedded HPC. This discussion naturally included KIT’s participation in EPI, which is why Prof. Jürgen Becker gave an interesting talk about the recent research activities in Germany and Europe also mentioning the on-goings in EPI and the known partners in the consortium. The project and plans were well received by the audience.

October schedule is still not finished, with several more events to go, all of which are announced at EPI’s web calendar: https://www.european-processor-initiative.eu/events/, serving as a perfect ramp-up to Initiative’s attendance at Supercomputing in Denver, US and EFECS conference in Helsinki, Finland in November. Meet us there!

Last week has been loaded with activities for the European Processor Initiative. Our team attended several very important events, where EPI was discussed and our road to the low-power processor presented.

EPI Chairman of the Board, Jean-Marc Denis, attended two events, in a Transatlantic hop, skip and a jump: first, the 73rd HPC User Forum in Chicago, where he presented EPI’s objectives and its interlink with the European Union’s EuroHPC Joint Undertaking, only to go back to Parallel Computing conference in Prague, with a similar mission. His talk concluded in presenting EPI’s challenges for the upcoming period: building on existing IP and communities and closing the gap between research and innovation and industrial products.

At the same time, beautiful cities of Bologna and Pisa hosted two events where the Initiative presented its objectives and roadmap.

In Bologna, at the Italian Workshop on Parallel and High-Performance Computing Technologies, the European Processor Initiative presented the EPI project to the Italian HPC academia and to the industrial users.

The academic participants presented their research lines and their previous engagement and contributions to EU programs, covering a wide spectrum of research fields and technological implementation. Andrea Bartolini (UniBO) presented the goals of the EPI, the members of the consortium and the roadmap for the processor, the accelerator and the automotive components, and highlighted the role of University of Bologna in the development of key components of the EPI project. Fabrizio Magugliani (E4 computer Engineering) presented the role of E4 in the development of key components of the EPI projects such as the PCIe daughter board hosting the EPI processor as Software Development Vehicle. The presentation opened a healthy discussion about how the community of Italian researchers could leverage the EPI project bringing the results of their research and therefore adding value to the project.

In Pisa, the EPI team participated at the RoundTable at ApplePies, 7th International Workshop Applications in Electronics Pervading Industry, Environment & Society. The Round Table confirmed that the EuroHPC Joint Undertaking, in full alignment with the objective of deploying in Europe a world-class supercomputing infrastructure and a competitive innovation ecosystem in supercomputing technologies, applications and skills by coordinating the efforts of its member states and share resources, has assigned one of the 3 Precursor to Exascale system to CINECA. Building on that, the Round Table’s participants presented the contribution of Italian-based institutions and enterprises towards the maximization of the results achieved through exascale-class systems both from the scientific and research point of view as well as from the industrial point of view. The current status of R&D in Italy specifically for the development of components for exascale-class systems was addressed, including the role of Italian institutions and enterprises in the European Processor Initiative (EPI) consortium, and which synergies among the key players could create a native Italian ecosystem fully aligned within the EuroHPC JU and EPI initiatives for enabling exascale-class systems to support scientific leadership and industrial competitiveness.

The week was finished by Atos team members participating at the Arm Research Summit in Texas, USA. Romain Dolbeau and Ying-Chih Yang gave a talk at the workshop “Impact of Arm hardware from an HPC application perspective (present and future-looking)”. The key objective of the workshop was gathering expertise from various research groups (runtime systems, linear algebra, operating system, performance modeling,…) to discuss key features and shape next-generation applications.

Partners from the European Processor Initiative organized and held their first public tutorial on EPI called “First steps towards a made-in-Europe high-performance microprocessor”. It was held on July 17th, at the Universita Politècnica de Catalunya, co-located with the ACM 2019 Summer school on HPC architectures for AI and dedicated applications.

EPI distinguished experts presented in front of a young and highly motivated audience, with more than 40 attendees in the audience. After a welcoming address by Fabrizio Gagliardi from BSC, presenters Andrea Bartolini (UNIBO), Mauro Olivieri (BSC), Jesús Labarta (BSC), Jaume Abella (BSC) and Francisco Cazorla (BSC) talked about the HPC landscape and the Initiative through several lectures.

The tutorial highlighted the challenges, trends on the processor’s technology in the High-performance computing market, and the opportunities for European technologies to play an active and leading role in the Exascale race.

The presenters explained why it was the right moment for a European computing platform and how EPI would address the challenge of creating an HPC platform which addresses the computing needs for future homogeneous and heterogeneous large-scale and autonomous driving automotive systems.

Presenter Andrea Bartolini, UNIBO, said after the tutorial: “It has been a pleasure to serve as the first presenter at the first EPI tutorial, co-organized at the ACM 2019 Summer school on HPC architectures for AI and dedicated applications on-going now in the beautiful Barcelona city. A new wave of young researchers and graduated students now know the challenges and opportunities which Europe is facing with EPI towards a made-in-Europe high-performance microprocessor.”

Presentations from the tutorial are available under the Dissemination and communication repository on EPI web, while the video materials of the tutorial are available at the EPI YouTube channel.

NVIDIA announced its support for Arm CPUs, by making available to the Arm® ecosystem its full stack of AI and HPC software — which accelerates more than 600 HPC applications and all AI frameworks – by year’s end.

The stack includes all NVIDIA CUDA-X AI™ and HPC libraries, GPU-accelerated AI frameworks and software development tools such as PGI compilers with OpenACC support and profilers.

Once stack optimization is complete, NVIDIA will accelerate all major CPU architectures, including x86, POWER and Arm.

Philippe Notton, general manager of EPI, said that the European Processor Initiative aims to endow the European Union with its own high-end, low-power, general purpose and accelerator solutions. EPI and SiPearl, its industrial hand, consider very positively the new possibilities offered by NVIDIA. The combination between the EPI Arm-based microprocessor and NVIDIA accelerator could make a perfect match for equipping building blocks in the future European exascale modular supercomputers.

The full article is available at nvidianews.

EPI’s first tutorial will be held on July 17th, at Universita Politècnica de Catalunya, Sala Ágora room, Plaça Telecos, North Campus UPC.

Distinguished experts from the Initiative will give lectures during a three-hour meeting on HPC processor landscape and EPI’s plans. The tutorial called “First steps towards a made-in-Europe high-performance microprocessor” is co-located with the ACM 2019 Summer school on HPC architectures for AI and dedicated applications.

Registration is now closed. Have a look at the attached agenda with all the necessary information.

We look forward meeting you at our first tutorial!

The European Processor Initiative (EPI), crucial element of the European exascale strategy, delivers its first architectural design to the European Commission and welcomes new partners

Almost six months in, the project that kicked off last December has already delivered its first architectural designs to the European Commission, thus marking initial milestones successfully executed. The project that will be the cornerstone of the EU’s strategic plans in HPC initially brought together 23 partners from 10 European countries, but has now welcomed three more strong additions to its EPI family.

EPI consortium aims to bring a low-power microprocessor to the market and ensure that the key competences for high-end chip design remain in Europe. The European Union’s Horizon 2020 program funds this project with a special Framework Partnership Agreement. The initial stage is a three-year Specific Grant Agreement, which lasts until November 2021.

The EPI consortium includes experts in all the relevant areas for such a major undertaking: the High-Performance Computing research community, major supercomputing centres, the computer system, automotive, and silicon industry, as well as the potential scientific and industrial users. Through a co-design approach, EPI will design and develop the first European HPC System for the HPC and automotive markets through several major streams of operation:

- HPC general purpose processor

- Accelerator

- Automotive platform

The Initiative is part of a broader strategy implemented by the European Union via its legal and funding entity – the EuroHPC Joint Undertaking (JU). The JU will enable pooling of the Union’s and national resources on HPC to acquire, build, and deploy in Europe the most powerful supercomputers worldwide.

EPI is one of the cornerstones of this EU HPC strategic plan. Drawing on the expertise of the partners in the consortium, EPI aims to bring a low-power microprocessor to market. It will ensure that the key competence of high-end chip and system design remains in Europe, a critical requirement for many application areas. Thanks to such new European-developed technologies, European researchers from academia and industry will be able to access HPC systems at exceptional levels of energy-efficient performance. As recognized by high-level EU officials, EPI will contribute to Europe’s scientific leadership, industrial competitiveness, engineering skills and know-how – not to mention society as a whole.

“European Processor Initiative will deliver key technologies to the new European HPC strategic plan for an independent and innovative European high-performance computing and data ecosystem. Energy efficient high-performance families of EPI processors will include most advanced general-purpose and accelerator cores that will deliver unprecedented processing capabilities, enabling EU researchers from academia and industry to most efficiently address global challenges. The business sustainability of the initiative is supported by carefully balanced target markets, with primary focus on exascale HPC/AI and automotive markets,” said Jean-Marc Denis, EPI Chairman of the Board.

“It is a privilege to lead this consortium and enable the creation of a new big player in the field of advanced semiconductors in Europe. We have the best teams, and a huge portfolio of expertise on board from deep node submicron, co-Design, computer science, to HPC, and automotive end-products. We expect to ship from 2021 our 1st high class and high-performance solution,” said Philippe Notton, General Manager of EPI.

“Acceleration is crucial to continued performance gains while reducing power consumption in computing. In EPI, the first accelerator will begin from RISC-V technology to deliver two unique vector and artificial intelligence accelerators for HPC and AI, since future supercomputers will be mostly heterogeneous; the second accelerator, based on Kalray’s IP, will lead the path to deterministic automotive computation. Both are offering a European solution to future global converged (HPC and AI) computing needs,” said Professor Mateo Valero, Director of Barcelona Supercomputing Center.

“The combination of general-purpose processors, hardware accelerators, security modules, and further IP modules on a system-on-chip is one of the key success factors for realizing a high-performant and energy-efficient automotive computing platform for autonomous driving and connected mobility”, said Matthias Traub, manager of electric/electronic architecture at BMW Group Research.

EPI will use a holistic approach to refine the system architecture and its component specifications. All aspects of the solution, and their interactions, will be considered and tackled simultaneously, taking a co-design approach:

- hardware platform architecture and components

- system and runtime software (OS, middleware, developers kit, compilers and libraries, etc.)

- HPC end-user applications

This approach will allow the consortium to meet the following goals:

- developing low-power microprocessor technology to be tentatively included in a European pre-exascale and subsequently exascale systems

- guaranteeing that a significant part of that technology is European,

- ensuring that the application areas of the technology are not limited only to HPC, but cover other areas such as the automotive sector and the data centers. Thus, ensuring the overall economic viability of the initiative. One specific objective for the automotive sector is to develop customized processors able to meet the performance needed for autonomous cars.

EPI plans to deliver two generations of processor families, with future families to follow. The architectural design of EPI processor families will ensure that individual processors address requirements specific to a particular market segment.

Full list of participating partners can be viewed here.

Impressions from the EuroHPC Summit Week 2019, that was held from 13 to 17 May in Poznań, Poland, are still fresh, as the event turned out a huge number of attendees and interesting topics covered in the 4-day event.

European Processing Initiative, under the moderating lead of Mr Leonardo Flores Añover and Mr Andrea Feltrin from DG CNECT, participated in a half-day workshop titled “Co‐designing with the European Processor Initiative”. The goals of the workshop were to identify applications that could drive co‐design for EPI and the pilot system projects; introduce attendees to co‐design for EPI and pilot system ideas leading to supercomputers based on EPI technologies; discuss component‐level vs. system‐level co‐design: who does what when; highlight ongoing co‐design efforts within EPI; bring application and technology/system architecture experts together; show the current status of the software landscape, and discuss how they can contribute to a coherent effort towards the European Exascale supercomputers.

Presenters from EPI covered those topics in 6 short presentations, while the session closed with an expert panel. Participants of the panel emphasized the importance of selecting a set of communities and involving them strongly in the co-design process. The communities should be those that really need Exascale performance, have high societal impact and are committed to participate in the co-design work. The systems in question will be heterogeneous and it is important to make them as user-friendly as possible; therefore, the middleware and programming environment play a very important role.

The panel also concluded that the use of HPC systems as workflows is increasing – they very often contain HPC with HPDA and AI. At Exascale level, workflows add an order of magnitude to the complexity. Using the sole general purpose processor combined at interposer level with many different accelerators helps drive the complexity down. EPI offers this unique feature. It is very important to provide middleware to properly support for workflows, also on heterogeneous systems.

The pilot system must demonstrate scalability, energy efficiency and reliability. Risks should be limited to a particular aspect/component of the system and the pilots should be operational, enable application running on them to prepare for Exascale, and provide results that increase visibility. The panel believes such visibility can be ensured through training as well – it is an opportunity to attract more people to the HPC field. It should be more attractive for young people, starting as early as school level. The panel concluded, looking to the future developments, that after Exascale, the goal should be not so much related to increasing speed, but making the Exascale systems much more efficient. Real-world application and workflow efficiency, as well as performance, need to be increased.