EPI, EUPILOT and EUPEX are joining forces at the Supercomputing24 conference, which is taking place in Atlanta, Georgia, USA, from November 17 – 22, 2024. The three projects will showcase their latest results and ideas at booth #4043.

AT THE BOOTH

Demo Pod

Filippo Mantovani and Pablo Vizcaino Serrano will present EPI’s and EUPILOT’s EPAC prototype featuring a RISC-V vector processing unit developed at the Barcelona Supercomputing Center (BSC). Schedule:

Tuesday, 19 November, 11:00 to 12:00pm EST

Wednesday, 20 November, 11:00 to 12:00pm EST

Thursday, 21 November, 13:00 to 14:00pm EST

Discussions

Researchers and representatives from various EPI consortium members will greet you at the booth to discuss the latest news in EPI development.

Specifically, the joint booth will organize a hot topic Question of the Day for Tuesday and Wednesday. The agenda is as follows:

- 15 minutes – Introduction of the EPI, EUPEX, and EUPILOT projects

- 5 minutes – Review the poll results (displayed live on the screen)

- 40 minutes – Open discussion moderated by the projects’ representatives

Tuesday – November 19, 2024, 3:00-4:00pm EST

TOPIC: What are the competitive advantages of Rhea1, SiPearl’s processor, designed as part of the EPI project? Participation link https://www.menti.com/al9zdpz6fbza

Wednesday – November 20, 2024, 3:00-4:00pm EST

TOPIC: What do you think is the biggest challenge for widespread adoption of RISC-V in the area of HPC? Participation link https://www.menti.com/als6c1a31r8a

Questions are open for voting already! Scan the QR code, or follow the link and share your opinion, regardless of whether you are attending SC24 (1-minute poll). If you are joining us at SC24 in person, come round to booth 4043 for live results and an engaging discussion on both day!

Program

Among other fascinating talks at SC24, EPI researchers will also take part in the workshops and symposiums. Make sure to catch it:

- Lilia Zaourar (CEA): A Co-Design Approach to NUMA Architectures in HPC: Quantitative Evaluation and Design Exploration. 10:30am – 10:50am EST, Sunday, 17 November 2024 at the Fourth International Symposium on Quantitative Codesign of Supercomputers, location B 304.

- Craig Prunty (SiPearl): SiPearl’s Rhea processor: high-bandwidth memory, ultimate solution for Large Language Models. 4:00pm – 4:30pm EST, Monday, 18 November 2024, at the Co-design of Next-Generation HPC Systems for Artificial Intelligence and Mixed-Analytics, location B314.

- Jens Kruger (Fraunhofer), Osman Unsal (BSC): European RISC-V based accelerators for HPC – overview and roadmap. 4:30pm – 5:00pm EST, Monday, 18 November 2024, at the Co-design of Next-Generation HPC Systems for Artificial Intelligence and Mixed-Analytics, location B314.

- Filippo Mantovani (BSC): BoF, at Advanced Architecture “Playgrounds” — Past Lessons, Current and Future Accesses of Testbeds. 12:15pm – 1:15pm EST, Thursday, 21 November 2024, location B309.

European HPC Passport Stamp Collection!

Take a European HPC passport and go! Here’s how it works:

- Collect Stamps – Pick up a stamp at each of the participating booths:

EuroHPC JU, LUMI/CSC, SiPearl, IT4Innovations, CIDS@TU Dresden, EPI/EUPILOT/EUPEX, ETP4HPC, PRACE, BSC, LRZ, HLRS, JSC, and CSCS/ETH Zürich.

- Enter the Drawing – Once your passport is fully stamped, show it at any participating booth to receive a raffle ticket for a chance to win exclusive prizes like Lego sets, Europa Stars sweaters, and more!

- Attend the Prize Drawing – Join us at the EuroHPC JU booth (#4249) on Thursday, Nov 21, at 11:30 am for the drawing. You must be present to win!

Collect, connect, and celebrate European HPC! Good luck and happy stamping!

On October 9 and 10, 2024, the European Processor Initiative organized and hosted its first EPI Forum in Barcelona, Spain.

The event was organized as a two-day conference, followed by an afternoon event organized by EUPEX project. More than 100 people attended the EPI Forum and participated in lively discussions, presentations and two panels.

The event was sponsored by six global technology providers: platinum sponsors included Arm, Eviden and NVIDIA, while AMD, Semidynamics and SiPearl were gold sponsors of the event.

After an introduction by Chairman of EPI Board, Eric Moncahlin, and a general overview of EPI given by project General Manager, Etienne Walter, the first day was opened by keynotes from notable speakers.

Director of BSC, Mateo Valero, spoke about the situation in Europe and the reasons for Buy versus Build when it comes to supercomputers, making a case for European sovereignty, and Stéphane Requena, CTO from GENCI, gave an insightful presentation about AI in Europe and infrastructure requirements, French ecosystem and GENCI’s work in the field.

The day continued with speeches from technology providers – Jean-Pierre Panziera from Eviden talked about HPC in the AI era, Eric Lalardie from Arm discussed Arm’s European activities and enabling European innovation, Daniele Piccarozzi from AMD presented his company’s solutions for HPC and AI, Philippe Notton, CEO of SiPearl, unveiled information about SiPearl’s Seine platform, while Roger Espasa, CEO of Semidynamics, gave a RISC-V-based perspective of his company’s All-in-One solutions for RISC-V AI.

The end of the first day was reserved for Arm and Rhea in high-end HPC, so EPI’s board member and SiPearl’s VP, Craig Prunty, gave an exhaustive presentation regarding key features of Rhea, GPP technology and exascale system for EPI. Following his view, Eric Monchalin introduced the end-day panel and panelists of the first day: Eric Lalardie, Jean-Pierre Panziera, Filippo Spiga from NVIDIA, Roger Espasa, Craig Prunty, Daniele Piccarozzi, Alexandra Kourfali from EuroHPC JU, and Etienne Walter. The group talked about the opportunities and risks in HPC ecosystem presented by the fact that innovation is driven with market demands which shifted towards cloud and AI, discussions about the importance of end-to-end co-design, costs of chip design, European sovereignty, and the ever-present need for sustainability and net-zero emissions.

The second day was opened by a keynote speaker from EuroHPC JU, Alenxandra Kourfali, who gave an interesting presentation on EuroHPC activities, chips initiatives, and the positioning of EPI in this environment. Her presentation was followed by NVIDIA’s take delivered by Rod Evans, who talked about the interesting concept of enabling development of AI in nations. The following segment was dedicated to RISC-V activities in EPI – and the EPI accelerator EPAC. Filippo Mantovani from BSC, EPI’s stream leader, gave an overview of EPAC and VEC, while Andrea Bocco from CEA and Tim Fischer from ETHZ talked about the variable extended precision accelerator for scientific computing applications and the Snitch core. David Snelling from Fujitsu gave a talk about Arm processor MONAKA in Fujitsu.

The day and the Forum closed with a panel on RISC-V future. It was moderated by Etienne Walter, EPI’s General Manager, and the panelists – Jean-Pierre Panziera, Daniele Gregori from E4, Manolis Marazakis from FORTH, Fabrizio Gagliardi from BSC, Alexandra Kourfalis Osman Unsal from BSC and Eric Monchalin, EPI’s Chairman of the Board – discussed about performance and scalability and how RISC-V compares to existing architectures like ARM, x86, etc., both now and in some predictions for the future. The panel also talked about the software ecosystem and whether the current one is mature enough to support large-scale HPC deployment on RISC-V. Panellists also offered their views on how the open-source nature of RISC-V would ensure standardization and avoid fragmentation in HPC implementations, ideas on cost and economic viability, energy efficiency and sustainability and IP issues – which relates to Europe’s strive for sovereignty.

The event was followed by EUPEX Forum presentations, which were open to all EPI Forum attendees to listen to free of charge.

All EPI Forum presentations are available in our repository here: https://www.european-processor-initiative.eu/dissemination-material/epi-forum-in-barcelona/, while highlight videos from presentations will be published on EPI YT channel here: https://www.youtube.com/@EuropeanProcessorInitiative.

Next year’s Forum will be held in Paris, stay tuned for more info!

The European Processor Initiative (EPI), a project with 27 partners from 10 European countries, with the goal of helping to achieve EU independence in HPC chip technologies and HPC infrastructure is proud to announce the first EPI Forum to be held in Barcelona, Spain, October 9-10, 2024.

Why attend?

For the first time, the largest project spearheading European efforts to power exascale supercomputers is inviting experts to meet and discuss progress, results and ways ahead for the European exascale processors and accelerators.

Attendees are expected to hear keynotes from industry leaders and champions in the field, keynote on AI by GENCI, keynote on Supercomputing by BSC and a keynote on the HPC future by EuroHPC as well as industry views from Platinum EPI Forum sponsors: Arm, Eviden, NVIDIA, and Gold EPI Forum sponsors: AMD, Semidynamics and SiPearl.

Forum will present an overview of EPI achievements and future plans including Rhea GPP, RISC-V based EPI accelerator cores and various applications. Each day will conclude with a panel discussion with distinguished panellists giving boarder views on presented topics.

EPI invites you to take part in this event, with EPI experts and global technology providers from all over the globe, shaping the future of HPC!

Registration

Registration is open at the EPI website: https://buy.stripe.com/14k3dz0OH9t40us9AA, and all other details regarding the event and policies are available on our website here: https://www.european-processor-initiative.eu/epi-forum-2024/

Venue

EPI Forum will be held in beautiful Barcelona, at the Barceló Sants hotel. The Forum will be organized in two days: the event starts on Oct 9 in the afternoon and continues with morning sessions on Oct 10. In the afternoon of Oct 10, our colleagues from EUPEX project will continue with their event at the same venue, which you can find out more about here: https://eupex.eu/events/eupex-forum-at-the-epi-forum/

We look forward to seeing you at the EPI Forum!

The 2024 edition of the ACM Summer School on HPC Architectures for AI and Dedicated Applications, organized by The Barcelona Supercomputing Center (BSC) and the Universitat Politècnica de Catalunya (UPC), will take place in Barcelona from 2-6 September 2024. This year’s program focuses on the convergence between HPC and AI, and it will also explore emerging research areas such as Quantum Computing. The school targets PhD and recent postdocs in HPC and AI. Exceptionally, outstanding MSc students with proven interest and/or experience in projects related to HPC and/or AI are also accepted. Participation in the school is free of charge. Sixty accepted participants will spend one week in Barcelona, attending formal lectures, invited talks, and other activities. The school will cover accommodation expenses and catering during school hours.

More information: https://europe.acm.org/seasonal-schools/hpc/2024

For another year, the entire European and global HPC community gathered to attend the ISC24 in Hamburg, Germany, seeing that it is likely the biggest and most important European HPC conference.

The theme was “Reinventing HPC into ISC 2024” and it was attended by more than 3,400 people in the Exhibition part, with more than 160 exhibitors at their respective booths.

The European Processor Initiative co-hosted a booth together with our colleagues from EUPEX and EUPILOT projects, where our tireless researchers and staff answered numerous questions about the activities in our project.

Colleagues from Barcelona Supercomputing Center, Filippo Mantovani and Fabio Banchelli Garcia, performed an EPAC prototype demo with a RISC-V vector processing unit, which garnered a lot of interest from participants.

On Wednesday, representatives from all three projects co-organized a Birds of Feather session called “European Processor Initiative & the Pre-Exascale Pilots”. The speakers were Pascale Bernier-Bruna (Eviden), Etienne Walter (Eviden), Carlos Puchol (BSC), and the session was moderated by Romana Konjevod (BSC). All three projects presented their goals in a short slide deck, and then opened the floor to a Q/A session. The BoF session had a full house, with many interested ISC attendees coming to participate in the discussion.

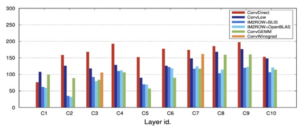

Collaboration among European research initiatives is crucial for the optimization of novel technologies and optimization of software. Thanks to the participation of Barcelona Supercomputing Center (BSC) and Polytechnic University of Valencia (UPV) researchers in the European eFlows4HPC and EPI projects, they developed optimised kernels for machine and deep learning (DL) operators that can replace the compute-intensive simulations in application workflows. EPI has provided a set of hardware/software tools for testing EPAC-VEC demonstrating that this technology can significantly accelerate the performance of the convolution.

After three years of research, the European project eFlows4HPC came to its end in February 2024. One of its target architectures was to investigate the benefits of novel computer architectures, such as the ones from EPI. eFlows4HPC experts optimized kernels for specific heterogeneous architectures. In particular, they optimised kernels on ARM-based architectures, equipped with “narrow” SIMD arithmetic units (single instruction, multiple data) arithmetic units, and RISC-V architectures, equipped with long vector processing units such as the one proposed in EPI, putting a strong emphasis on portability.

In addition, BSC and UPV experts migrated some of the computational kernels in the eFlows4HPC workflows to the EPI. eflows4HPC experts tested SVD on EPI hardware obtaining a clear the reduction of execution time from using the VPU (vector version of the routines) compared with an execution only using the RISC-V core (scalar version).

One of the eFlows4HPC Key Exploitable results (KER) is Convolution operators on multicore ARM and RISC-V architectures (CONVLIB), fully developed by UPV. CONVLIB is a library containing high performance implementations of convolution algorithms for multicore platforms with ARM and RISC-V architectures. It contains a driver routine that identifies the best values for four hyper-parameters: micro-kernel, cache configuration parameters, parallelization loop and algorithm, automatically adapting the call to the dimensions of the convolution operator. At EPAC-VEC level, UPV researchers in collaboration with BSC experts migrated ConvLIB to exploit the VPU accelerator in this architecture showing that the EPAC-VEC can significantly accelerate the performance of the convolution. “These experiments show that the EPAC-VEC can significantly accelerate the performance of the convolution, but it does require a very careful implementation of the codes”, states Enrique S. Quintana, UPV professor and eFlows4HPC work package leader. This library is now available at the open software repository here: https://github.com/hpca-uji/ConvLIB

The results of this research have also been published in the following peer-reviews publication:

Ramírez, A., Castelló, and E. S. Quintana-Ortí, “A BLIS-like matrix multiplication for machine learning in the RISC-V ISA-based GAP8 processor,” J. of Supercomputing, 2022. https://doi.org/10.1007/s11227-022-04581-6.

About eFlows4HPC

eFlows4HPC is a European-funded project with a budget of €7.6M that started on 1 January 2021 and lasted 3 years and 2 months. Coordinated by BSC (Spain), the project brings together a multidisciplinary consortium: CIMNE (Spain), FZJ (Germany), UPV (Spain), ATOS (France), DtoK Lab (Italy), CMCC (Italy), INRIA (France), SISSA (Italy), PSNC (Poland), UMA (Spain), AWI (Germany), INGV (Italy), ETHZ (Switzerland), Siemens (Germany), and NGI (Norway).

The eFlows4HPC project has received funding from the European High-Performance Computing Joint Undertaking (JU) under grant agreement No 955558. The JU receives support from the European Union’s Horizon 2020 research and innovation programme and Spain, Germany, France, Italy, Poland, Switzerland, Norway. It also received funding from MCIN/AEI/10.13039/501100011033 and the European Union NextGenerationEU/PRTR (PCI2021-121957).

EuroHPC Summit 24, a conference gathering European key stakeholders and users in the high-performance computing field, was held from March 18 to March 21, 2024, in Antwerp, Belgium.

The conference gathered more attendees than ever before, who were eager to see that is new in the European HPC space and perhaps eager to visit poster sessions, demos or finally, get a special look into the work of European supercomputers.

The European Processor Initiative was present at the event. Our CCO, Mario Kovač, attended the poster sessions explaining how far along we are in the project timeline.

Colleagues from Barcelona Supercomputing Centre showcased the EPAC chip, the first RISC-V based prototype leveraging vector acceleration coming from the EPI project.

EPI’s General Manager, Etienne Walter, and SiPearl’s CEO and founder, Philippe Notton, attended the parallel sessions on European Chip Initiatives for HPC, where they gave a detailed overview of what EPI is doing right now and what kind of developments can be underway for Rhea1 and Rhea2 processors.

On July 19th, the Council Regulation establishing the European High-Performance Computing Joint Undertaking was published in the Official Journal of the European Union. It was formally adopted on July 13th, by the Economic and Financial Affairs Council.

This is an important piece of news for the HPC community, opening up EuroHPC JU’s ability to draw funds from the Horizon Europe, Digital Europe and the Connecting Europe Facility programmes. The news item and full regulation text can be found on the EuroHPC JU’s website, here:

Taking place on 30 August – 3 September 2021, the second ACM Europe Summer School on HPC Computer Architectures for AI and Dedicated Applications will be co-hosted by Barcelona Supercomputing Center (BSC), in conjunction with the Universitat Politècnica de Catalunya – Barcelona Tech (UPC).

The programme of this year’s summer school, which will be fully remote, centres around topics within the European Processor Initiative. Open hardware expert Luca Benini (ETH Zürich / University of Bologna) will be discussing machine learning from a RISC-V platform perspective, while the EPI Accelerator stream leader Jesús Labarta (BSC) will train attendees in performance analysis and hybrid programming, helping them get the very best out of their code. Meanwhile, Mauro Olivieri (Sapienza – University of Rome / BSC) will present vector acceleration in high-performance computing (HPC) and edge devices.

Keynote talks will be given by celebrated computer scientists and engineers including Luca Cardelli (Oxford University), Bill Dally (Stanford University / NVIDIA), Mihaela van der Schaar (Cambridge University) and Mateo Valero (BSC). There will also be invited talks by EPI researchers Roger Espasa (Semidynamics) on the RISC-V Avispado core, John Davis (BSC) on building an open-source ecosystem for HPC, and Marc Casas (BSC) on accelerating deep neural network training.

The school chairpersons are Mateo Valero and Josep Fernandez (UPC), while the local organizing committee is led by Eduard Ayguadé, (BSC and UPC), and Fabrizio Gagliardi (BSC and ACM).

“EPI is revolutionising computer architecture to pave the way for Europe’s technological sovereignty. As part of the EPI training programme, this summer school provides the ideal introduction to some of the initiative’s main themes,” commented Jean-Marc Denis (Atos / SiPearl), chairman of the EPI board.

Upon completion of the school, all attendees will receive a certificate and a complimentary ACM student membership. Based on the scores obtained in the practical exercises, the best performing students will receive a certificate of honour and will also invited to interviews with industry sponsors, with a view to a possible internship.

The school includes a poster session, with a prize for the best poster.

Registration will be open until 15 July, and accepted candidates will be informed by 1 August.

To register, complete the registration form on the ACM Europe website.

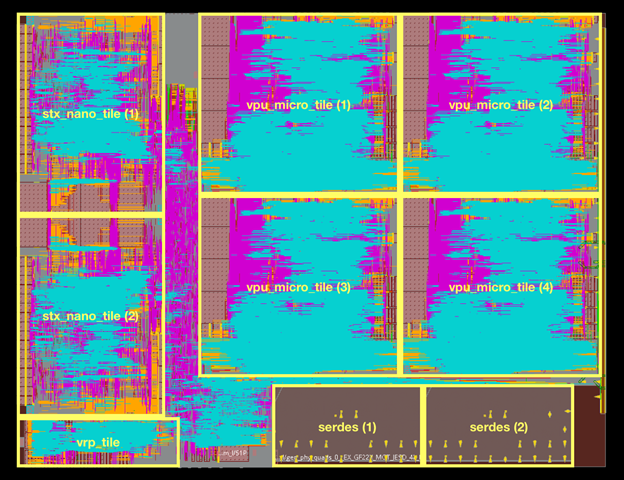

The Initiative has successfully released EPAC1.0 Test Chip for fabrication

The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 28 partners from 10 European countries, with the goal of helping the EU achieve independence in HPC chip technologies and HPC infrastructure, is proud to announce that we have successfully released our EPAC1.0 Test Chip for fabrication.

One key segment of EPI activities is to develop and demonstrate fully European-grown processor IPs based on the RISC-V Instruction Set Architecture, providing power-efficient and high-throughput accelerator cores named EPAC (European Processor Accelerators). Using the RISC-V Instruction Set Architecture will allow leveraging open-source resources at hardware architecture and software level, as well as ensure independence from non-European patented computing technologies.

EPAC combines several accelerator technologies specialized for different application areas. The test chip, shown in figure 1 below, contains four vector processing micro-tiles (VPU) composed of an Avispado RISC-V core designed by SemiDynamics and a vector processing unit designed by Barcelona Supercomputing Center and the University of Zagreb. Each tile also contains a Home Node and L2 cache, designed respectively by Chalmers and FORTH, that provide a coherent view of the memory subsystem. The Stencil and Tensor accelerator (STX) was designed by Fraunhofer IIS, ITWM and ETH Zürich, and the variable precision processor (VRP) by CEA LIST. These specialized accelerators are connected with very high-speed network on chip and SERDES technology from EXTOLL.

The EPAC design was finalized by Fraunhofer IIS for chip integration in GLOBALFOUNDRIES 22FDX low-power technology and will be integrated and evaluated in the FPGA-based board designed by FORTH, E4 and the University of Zagreb. The successful fabrication of EPAC will showcase the next step in accelerator-based green HPC computing.

The outlook

The next generation of the EPAC accelerators and interfaces will be improved and refined for even higher performance and lower power levels in 12 nm technologies and below, and by adding a chiplet approach.

Jesus Labarta, BSC (EPAC Coordinator): I am really happy how partners with different backgrounds and motivations have been able to collaboratively develop this chip, putting all their efforts towards a collective success. It is a fully European design, driven by a vision of throughput-oriented computing and featuring characteristic that will result in high programmer productivity and achieve very high performance at low power and cost. Although just an initial Test Chip, it can be a significant step forward in HPC but also for edge and embedded applications.

Norbert Schuhmann, Fraunhofer IIS: The key challenge in this design and architecture was not only to achieve highest throughput and low power levels within the accelerators running on more than 1 GHz, but also to be in sync like in a concerto with memory accesses and data transport inside the chip and to the peripherals at rates above 200 Gbit/s.