Exascale computation systems will need to simultaneously meet challenges related to performance, system cost, and energy efficiency. To deliver performance, a vast amount of resources is required, but the wrong choices of components, architecture, or implementation might result in a system which is much too expensive and too power-hungry. To find the right balance, global system level optimization is necessary.

GPP Stream

EPI, therefore, intends to share a strong set of common technology across different application domains. Starting from the selection of cutting-edge process technology, a low-power design approach ranges from massive parallelism, specialized architecture, low-voltage operating point, and fine grain power management. The software stack will be designed to integrate and take advantage of these features to achieve high-energy efficiency and maximize performance across a wide range of layers from the low-level firmware, all the way up to system software and application run-times. For this purpose, EPI will harmonize the heterogeneous computing environment by defining a common approach: the so-called Common Platform (CP). It will include the global architecture (hardware and software) specification, common design methodology, and global approach for power management and security.

The CP is organized around a 2D-mesh Network-on-Chip (NoC) connecting computing tiles based on high-performance general-purpose CPU core with built-in FPU acceleration and specialized application-accelerators with different acceleration levels designed within EPI project.

A common software environment between heterogeneous computing tiles will harmonize the system as well as acting as a common backbone of IP components for IO connection with the external environment such as memories and interconnected or loosely coupled accelerators. With this CP approach, EPI will provide an environment that seamlessly integrates any computing tile. The right balance of computing resources for application matching will be defined through the ratio of the accelerator and general-purpose tiles.

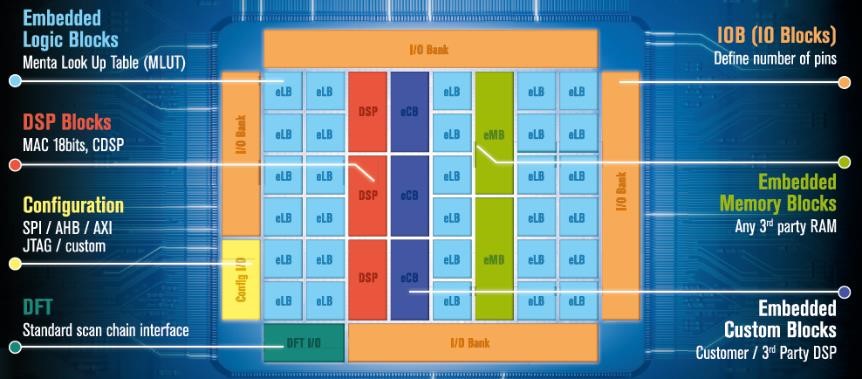

EPI embedded FPGA eFPGA

The eFPGA tile, which is integrated into the General Purpose Processor chip (GPP), contributes to an energy-efficient allocation of the necessary performance by an optimal interaction with the main CPU and the dedicated Hardware accelerators.

Menta eFPGA IP is optimized for general purpose HPC and automotive applications such as image-processing using machine learning (ML). It allows post-production functions like customer customization and proprietary elements. In addition, it can consider emerging security aspects, like run-time reconfigurable crypto and post-quantum public crypto accelerators.

The eFPGA core plays a key role in an optimal hardware/software codesign system, enabling reconfiguration options for the next generation of the European HPC and automotive industry.

Hardware acceleration features are moved on-chip, without the limitations or overhead due to I/O pad-count or chip-to-chip communication interfaces. The eFPGA core is provided to EPI customers with the corresponding programming software-tool, Origami Programmer, which generates the bitstream that targets and optimizes RTL to the needs of Menta eFPGA architecture. The technology does not rely on third-party software tools, which target generic FPGA architecture and thus deliver suboptimal results.