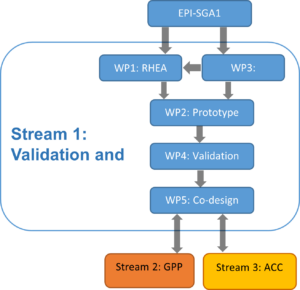

In EPI SGA2, work on the “Common Platform” (common to the GPP & Accelerator streams) will be further developed at hardware and software levels in continuation of EPI SGA1.

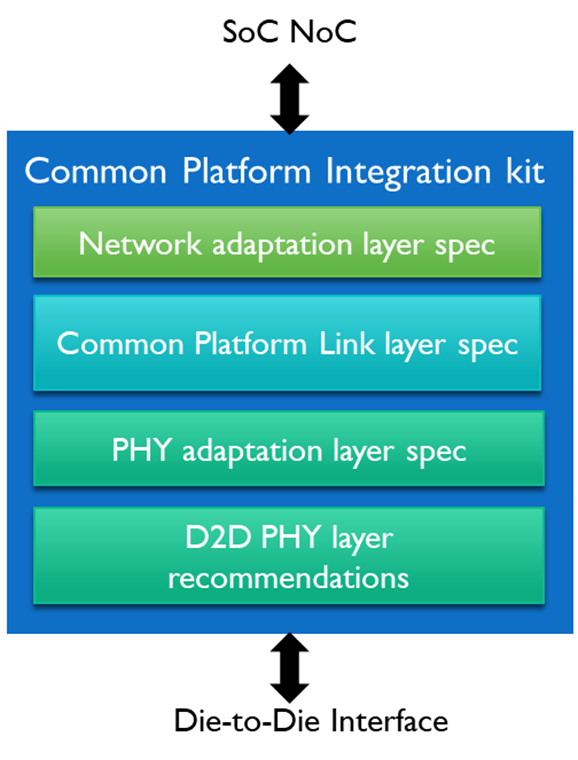

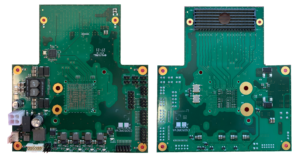

Stream 2 will produce the specification that defines the hardware Common Platform for the chip and system integrating technologies to address the need for designing decoupled systems combining hybrid compute units, with closely coupled performance and ease of use.

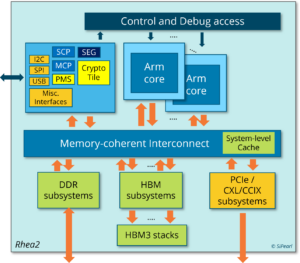

Use cases will be studied to specify requirements for the hardware Common Platform Architectural specification. As part of these activities, interfaces such as the latest CXL, CCIX, and PCIe will be considered. Specifically, CXL will offer memory and I/O coherency, lower latency than PCIe and future proofing. Moreover, we will analyse die-to-die interfaces for chiplet-chiplet interconnects: BOW, UCIe, and XSR are some of the candidate solutions to be analysed for performance as well as expected industry acceptance and availability.

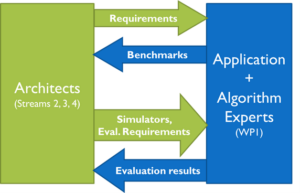

From a software perspective, the objectives of the Common Platform are to elaborate an ecosystem and a set of methods and tools to program accelerators seamlessly across socket-socket or die-to-die interfaces. This will be achieved by selecting or developing standards for connections between heterogeneous elements including software support for physical interconnects, SW orchestration, and support for memory coherency. This will enable the development of generic programming approaches that ensure code portability and performance portability, and ultimately aid performance testing on HPC platforms offering different processor technologies.

The expected achievements consist in aligning with, modifying, or building a standard for hardware Common Platform implementing the software flow to offload computing tasks to accelerator units and the related accelerator software flow.